#### Roberto Silva Cantanhede

## $Suporte\ a\ simulação\ distribuída\ em\ System C$

Orientador: Ricardo Pezzuol Jacobi

Universidade de Brasília Departamento de Ciência da Computação Mestrado em Informática - Programa 2004 Início do programa: Março/2004 PNM: Agosto/2005

Sub-área no PNM: Modelagem de dispositivos

Dissertação de Mestrado sob o título "Suporte a simulação distribuída em SystemC", defendida por Roberto Silva Cantanhede e aprovada em 23 de maio de 2007, em Brasília, Distrito Federal, pela banca examinadora constituída pelos doutores:

Prof. Dr. Ricardo Pezzuol Jacobi Orientador

Prof. Dr. Diógenes C. da Silva Júnior UFMG

Prof. Dr. Marcos Vinicius Lamar Universidade de Brasília

## Resumo

A contínua evolução tecnológica da microeletrônica viabiliza a integração de sistemas cada vez mais complexos em dispositivos semicondutores. Os sistemas integrados monolíticos (SoC - Systems on Chip) atuais permitem a integração de processadores, memórias e módulos dedicados analógicos, digitais e de radio-freqüência em uma única pastilha de silício. A simulação de tais sistemas é uma etapa fundamental no desenvolvimento de um SoC, pois permite a verificação de sua funcionalidade antes do detalhamento de sua implementação. A disponibilização de modelos simuláveis dos elementos de processamento de um SoC já nas primeiras etapas do projeto é igualmente fundamental para acelerar o processo de desenvolvimento do software embarcado, permitindo que o código produzido possa ser executado e testado de forma concorrente ao projeto do hardware.

A redução do tempo de simulação afeta diretamente o ciclo de projeto do SoC, visto que impacta tanto no desenvolvimento do hardware quanto no do software embarcado. Um dos fatores limitantes na aceleração da simulação é a utilização de sistemas monoprocessados. Tipicamente, uma descrição de um SoC é compilada e executa em um computador monoprocessado que simula por software o paralelismo do hardware. Uma forma de se atingir o objetivo de acelerar a simulação de sistemas em silício é a executação concorrente dos módulos do sistema. Assim, em vez dos módulos serem simulados em um único processador, eles podem ser distribuídos entre nodos de um *cluster* de computadores, sendo simulados com paralelismo real.

O objetivo deste trabalho é o estudo da introdução de processamento concorrente em sistemas integrados descritos em SystemC. Essa linguagem atingiu, ao longo dos últimos anos, o status de padrão para descrições em nível de sistema. Baseia-se em C++, introduzindo conceitos de orientação a objetos na descrição do hardware. Neste trabalho é proposta a paralelização da simulação de sistemas descritos em SystemC pela distribuição de módulos entre processos de um sistema multiprocessado. A comunicação entre módulos SystemC se realiza através de filas não bloqueantes, sendo a troca de mensagens entre processos implementada através do protocolo TCP/IP.

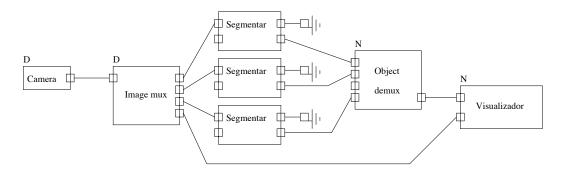

Como estudo de caso para simulação concorrente foi estudado e descrito em SystemC um algoritmo de segmentação de imagens, que serve como base para métodos para deteção de movimento em seqüências de imagens a ser implementado em um SoC para redes de sensores em desenvolvimento no contexto do projeto NAMITEC. Apresenta-se o algoritmo de segmentação e os resultados de sua simulação em SystemC.

## Abstract

The ever increasing evolution of microelectronics allows the integration of more and more complex systems in semiconductor devices. Present day System on Chip (SoC) may integrate processors, memories, analog, mixed-signals, digital and RF modules in a single chip. The simulation of a SoC is a fundamental step in system design, since it permits the verification of its funcionality before dwelling on the details of the hardware design. The availability of simulation models for the processing elements early in the design process is also important for the embedded software development, which may then occur concurrently to hardware design.

The reduction of simulation time have a direct impact on the design cycle time, affecting both the hardware and the software development. The use of monoprocessor platforms for simulation is a limiting factor in the search of simulation speed up. Tipically, the SoC description is compiled and executed in a single process, where the hardware parallelism is simulated by software. One possible way to reduce simulation time is the parallel execution of the hardware models. Instead of being simulated in a single process, the modules may be distributed among nodes of a cluster which execute them in parallel.

The goal of this work is to study the introduction of concurrent processing in the simulation of SoC described in SystemC. This languagem attained the status of a standard for system level modeling last years. It is based on C++, introducing object oriented concepts in the hardware modeling. The poposal of this work is to paralelize the simulation by distributing SystemC modules among different processes in a multiprocessor system. The communication among those modules is performed through non-blocking fifos and is implemented over the TCP/IP protocol.

A case study was developed for verification purposes. It consists in the implementation of a image segmentation algorithm to be used as support for image detection in video sequences, as part of the research project NAMITEC which targets the development of a SoC for sensor networks. The image segmentation algorithm and the simulation results in SystemC are presented.

## Sum'ario

#### Lista de Tabelas

#### Lista de Figuras

| 1 | Intr | rodução                                                                   | p. 9  |

|---|------|---------------------------------------------------------------------------|-------|

|   | 1.1  | Objetivo                                                                  | p. 9  |

|   | 1.2  | Projeto de sistemas digitais                                              | p. 10 |

|   | 1.3  | SystemC                                                                   | p. 13 |

|   | 1.4  | Justificativa                                                             | p. 19 |

| 2 | Mo   | delagem em SystemC de sistemas em silício                                 | p. 22 |

|   | 2.1  | Caracterização dos modelos mais comuns                                    | p. 22 |

|   | 2.2  | Implementação de alguns modelos em SystemC                                | p. 26 |

| 3 | Sim  | ulação distribuída                                                        | p. 34 |

|   | 3.1  | Processo de paralelização                                                 | p. 38 |

|   | 3.2  | Aplicação do processo de paralelização                                    | p. 39 |

|   |      | 3.2.0.1 Decomposição em tarefas                                           | p. 40 |

|   |      | 3.2.0.2 Atribuição de tarefas aos processos, coordenação e de-<br>legação | p. 41 |

|   | 3.3  | Opções de implementação                                                   | p. 42 |

|   | 3.4  | Implementação                                                             | p. 43 |

|   |      | 3.4.1 Recursos utilizados                                                 | p. 43 |

|   |      | 3.4.2 Comunicador UDP                                                     | р. 46 |

|   |       | 3.4.3   | Comunicador TCP                                    | p. 47 |

|---|-------|---------|----------------------------------------------------|-------|

|   |       | 3.4.4   | Módulos de apoio                                   | p. 50 |

|   |       | 3.4.5   | Módulos dispositivo                                | p. 51 |

|   |       | 3.4.6   | Módulos não-SystemC                                | p. 51 |

| 4 |       |         | e caso: Modelagem e simulação de um segmentador de | n 59  |

|   | ıma   | gens    |                                                    | p. 53 |

|   | 4.1   | Arqui   | tetura                                             | p. 53 |

|   | 4.2   | Descri  | ição do algoritmo                                  | p. 55 |

|   | 4.3   | Imple   | mentação do algoritmo                              | p. 57 |

|   |       | 4.3.1   | Resultados                                         | p. 60 |

|   |       | 4.3.2   | Críticas da implementação                          | p. 63 |

| 5 | Cor   | ıclusão |                                                    | p. 65 |

| R | eferê | ncias   |                                                    | p. 67 |

## Lista de Tabelas

| 1 | Tabela comparativa dos modelos de descrição de hardware (*) variáveis  |       |

|---|------------------------------------------------------------------------|-------|

|   | compartilhadas, métodos ou funções                                     | p. 26 |

| 2 | Resultados do modelo funcional temporizado                             | p. 32 |

| 3 | Tempos de transmissão por carga útil. *38 bytes do ethernet, 20 do TCP |       |

|   | e 12 do IP                                                             | p. 44 |

| 4 | Resultados do cenário envolvendo o módulo de exibição e de transmissão |       |

|   | de imagens                                                             | p. 61 |

| 5 | Resultados do cenário envolvendo a arquitetura completa apontando mí-  |       |

|   | nimos e máximos obtidos.                                               | p. 62 |

| 6 | Resultados para segmentação e exibição em um único processo            | p. 63 |

| 7 | Resultados para segmentação e exibição em dois processos em computa-   |       |

|   | dores distintos                                                        | р. 64 |

## Lista de Figuras

| 1  | Modelo do "U" invertido utilizado no BrazilIP                                                                                                                                           | p. 35 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 2  | Exemplo de acumulação do <i>overhead</i> de comunicação no tempo total de simulação                                                                                                     | p. 39 |

| 3  | Exemplo de acumulação do <i>overhead</i> de comunicação bidirecional no tempo total de simulação                                                                                        | p. 39 |

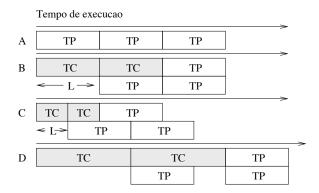

| 4  | (A) Tempo de Processamento TP de 3 transações; (B) TP igual ao Tempo de Comunicação TC com L indicando a latência; (C) TC menor que TP, reduz o tempo de execução e (D) TC maior que TP | p. 41 |

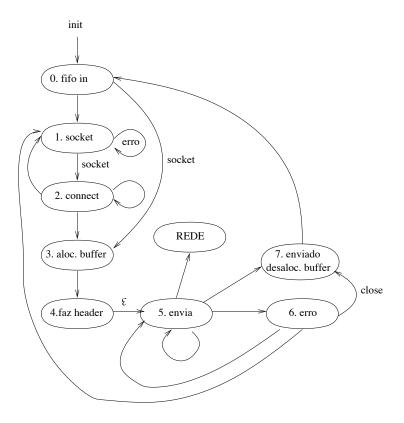

| 5  | Máquina de estados simplificada do módulo TCPFIFO_OUT                                                                                                                                   | p. 48 |

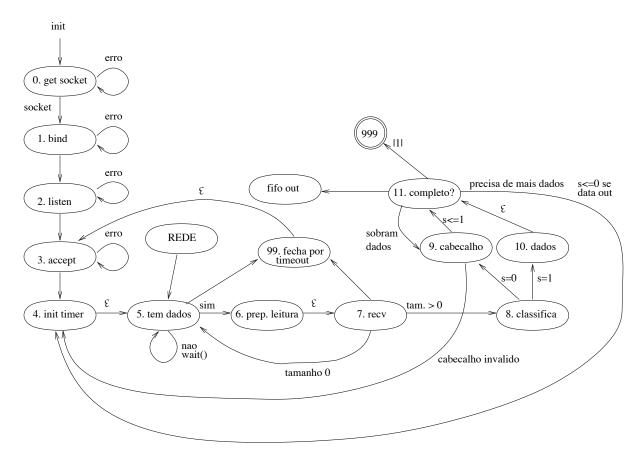

| 6  | Máquina de estados simplificada do módulo TCPFIFO_IN                                                                                                                                    | p. 49 |

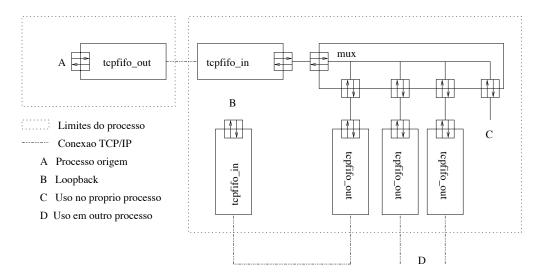

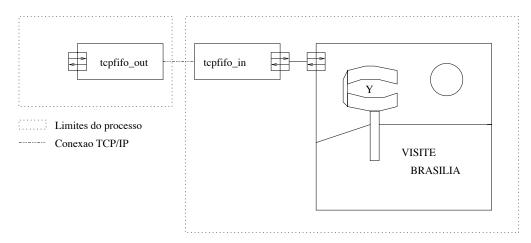

| 7  | Ilustração de uso do comunicador TCP                                                                                                                                                    | p. 50 |

| 8  | Ilustração de uso do comunicador TCP em uso como dispositivo, integrando simuladores                                                                                                    | p. 51 |

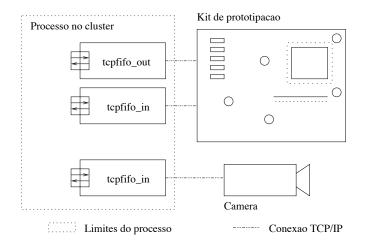

| 9  | Ilustração de uso do comunicador TCP integrando dispositivos                                                                                                                            | p. 52 |

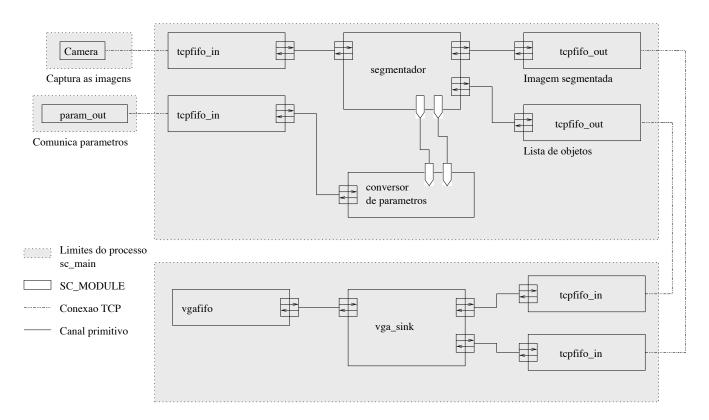

| 10 | Arquitetura mínima do segmentador, com paralelismo entre tarefas    .  .                                                                                                                | p. 54 |

| 11 | Cena de dormitório                                                                                                                                                                      | p. 59 |

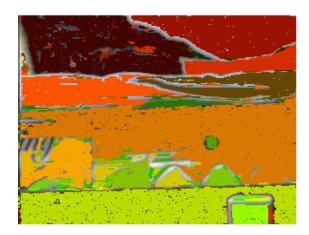

| 12 | Cena de dormitório em segmentos, exemplificando os segmentos da imagem                                                                                                                  | p. 60 |

| 13 | Cenário 1: interação entre um processo e um simulador                                                                                                                                   | p. 61 |

| 14 | Cenário 2: interação entre 7 simuladores                                                                                                                                                | p. 62 |

## 1 Introdução

#### 1.1 Objetivo

O desenvolvimento de sistemas digitais é uma tarefa bastante complexa. é necessário elaborar a especificação do sistema, levantar os algoritmos que serão utilizados, decidir que plataforma utilizar para a implementação, elaborar a bancada de testes, implementar e testar cada parte, integrar o sistema, testar a integração até chegar a produção da primeira unidade. Esse processo é dispendioso e necessita de ferramentas especializadas para que cada etapa seja concluída com sucesso.

Para que um sistema digital seja modelado eficientemente, é possível utilizar uma hieraquia de modelos com diferentes níveis de abstração, onde as otimizações realizadas em cada nível proporcionam ganhos ao processo todo. Nos estágios iniciais é preferível que não se perca tempo definindo minúcias do hardware final, mas concentrar esforços na sua funcionalidade. Nesse momento a simulação de um modelo abstrato em alto nível de abstração traz benefícios para todo o projeto pois permite ter estimativas da complexidade e custo finais do sistema, bem como esboçar um método de teste.

Para tentar otimizar os passos de teste e integração, neste trabalho será apresentado um módulo que implementa comunicação entre dois pontos (comumente processos do sistema operacional) via protocolo TCP e permite que recursos de software e hardware em nós físicos, como computadores ou kits de prototipação, distintos sejam utilizados na simulação como um único sistema digital. A viabilidade dessa implementação depende da ferramenta usada como base para a execução de testes e integração e do tipo de comunicação envolvida entre os nós que se comunicam.

A validação será realizada através de um estudo de caso que permita executar os simuladores em paralelo e realizar a injeção de dados de processos externos dentro do sistema simulado.

#### 1.2 Projeto de sistemas digitais

A qualidade das ferramentas utilizadas no processo de desenvolvimento de um sistema e sua facilidade de uso são fatores que podem ser decisivos no tempo de desenvolvimento de um produto. Se a ferramenta for excelente mas tiver uma curva de aprendizado pouco suave pode tornar proibitivo o tempo gasto no seu aprendizado. Quanto mais rápido o desenvolvedor se torna familiar ao seu ambiente de trabalho, melhor seu desempenho em propor soluções dentro do domínio dos elementos da linguagem.

Nesse contexto, considerando que as linguagens de programação estruturadas (e até as orientadas a objeto) de alto nível como Java, C, C++ e Pascal tem estruturas muito semelhantes e têm uma base de conhecimentos ampla e bem disseminada, aproveitar para a descrição do hardware todos os recursos que essas linguagens oferecem pode proporcionar ganhos não só para os desenvolvedores mas para todo o processo de desenvolvimento. Entretanto, essas linguagens, como se apresentam, não são adequadas para descrever sistemas em hardware.

Sistemas em software geralmente são escritos usando linguagens de alto nível descrevendo algoritmos seqüenciais. O desenvolvimento de algoritmos na forma seqüencial está vinculado ao paradigma de computação inerente ao modelo von Neuman: armazenar o código do programa numa memória, que é lido por um processador que o executa seqüencialmente e possivelmente escreve o resultado desse código de volta na mesma memória. Como conseqüência das escritas em memória um dispositivo que faz E/S por memória mapeada ou que funciona bisbilhotando o barramento de memória (como as snoop caches) pode apresentar um resultado em um outro dispositivo de saída ou sinalizar que o programa deve aguardar que um dispositivo esteja pronto. O desempenho de um sistema em software depende essencialmente do somatório dos tempos de suas instruções, tempo de espera por dispositivos, número de iterações (repetições) e número de interações. Existem otimizações arquiteturais que podem promover a execução paralela de instruções, mas este não é um recurso do sistema em software, é algo alcançado com suporte sofisticado do hardware.

Sistemas em hardware, por outro lado, podem definir suas saídas diretamente a partir das entradas (lógica combinacional) ou a partir de alguma combinação de entradas sucessivas e estados internos (lógica seqüencial). A computação é realizada executando um software (isto é, lendo, decodificando e executando instruções armazenadas em uma memória) ou implementando diretamente o algoritmo em hardware através da composi-

ção de módulos combinacionais e seqüenciais. No hardware, os sinais são alimentados de forma concorrente e podem armazenar resultados em estruturas intermediárias, como registradores e buffers. Para determinar o tempo gasto entre o estímulo do sistema e sua resposta é necessário medir o atraso físico dos sinais. O atraso dos sinais é influenciado por diversos fatores físicos como capacitância, indutância, temperatura, diferença de potencial e materiais utilizados para a construção do circuito. As saídas do sistema são calculadas com base em operações lógicas distribuídas no espaço físico da implementação. Embora mais eficientes do que as implementações em software, são inflexíveis pois uma vez que seu comportamento está definido, e o hardware é fabricado, ele não muda. A excessão são os sistemas configuráveis onde a exploração espacial dos operadores pode ser reorganizada por conexões programáveis, e logo esses dispositivos, situados entre os extremos dos sistemas em software e os sistemas em hardware, possuem parâmetros como tamanho de grânulo e número de conexões programáveis, bem como outras variáveis que os distinguem e proporcionam um terceiro eixo para uma possível comparação, que não abordamos neste trabalho.

Dadas as diferenças entre os sistemas de software e de hardware, as linguagens usadas para descrever um e outro são diferentes. Enquanto um software é geralmente escrito para uma arquitetura com um conjunto de instruções, um sistema de hardware descreve uma distribuição espacial física de componentes. Para chegar nesse sistema físico implementado de forma controlada e previsível é necessário construir modelos (ou protótipos) desse sistema e refiná-los conforme amadurecem ou ainda especificá-los e implementá-los sem prototipação [14]. Adotamos a abordagem da prototipação.

Um modelo de um sistema de hardware pode ser escrito em diferentes níveis de abstração, alguns com extrema riqueza de detalhes como o RTL e outros com características mais gerais, como o TLM. Esses modelos serão abordados oportunamente. Os níveis mais altos são muito semelhantes ao software, entretanto, cabe diferenciá-los. Um software é uma transcrição de um conjunto de algoritmos (como algoritmos de ordenamento, escalonamento e decisão) e de modelos computacionais (redes de Petri, autômatos, dataflows, eventos discretos) para execução em uma plataforma qualquer. Um modelo de hardware pode prover desde a plataforma para a execução do software até um sistema completamente discreto com um ou mais modelos computacionais implementados. Para o hardware, pode ser mais fácil ou mais complexo, transcrever os algoritmos em componentes discretos ou em algoritmos. Tudo depende do nível de detalhamento do hardware que se queira expressar no modelo. Além do nível de detalhamento, deve-se levar em conta outras variáveis como ciclo de vida do produto final, seu custo de produção e de gerações

futuras.

Assumindo que os modelos computacionais e linguagens de alto nível são elementos conhecidos, uma linguagem para descrição de hardware tem, em síntese e para diferenciála de linguagens comuns à geração de software, características como [7]:

- descrever o dispositivo em diferentes níveis de abstração;

- dar suporte ao paralelismo do hardware;

- introduzir a noção de sinal elétrico;

- modelagem da temporização;

- incorporar software da plataforma desenvolvida em diversos níveis;

- prover um modelo executável;

- permitir exploração de arquiteturas;

- ter um simulador eficiente e rápido e separar comunicação do sistema de processamento.

Em muitas linguagens de programação, usadas amplamente para os processadores de uso geral, falta suporte, por exemplo, para estruturas físicas básicas como fios e elementos mais elaborados como construções paralelas, típicas de qualquer sistema implementado em chips e característico de todos os níveis de abstração de hardware. Isso dificulta a simulação especialmente nos níveis mais baixos. Os sistemas implementados em silício são paralelos sempre, no sentido de que uma vez alimentados os transistores que implementam as operações lógicas ele sempre estará funcionando. Desativar individualmente um conjunto de transistores e deixá-los desativados durante o funcionamento do sistema é contraproducente, uma vez que os transistores ociosos consomem recursos de energia e demandaram capital para sua produção. Quanto melhor o uso do sistema como um todo, mais eficiente é a solução em termos de uso da área de silício [5].

Para explorar o paralelismo característico do hardware, é desejável que as linguagens utilizadas para sua construção proporcionem meios eficientes para modelar esse paralelismo. Em Java, temos uma classe que implementa a concorrência (Thread). Para outras linguagens temos bibliotecas responsáveis por essa abstração e até padrões para a implementação de processos paralelos, como o POSIX [10]. Ainda que a linguagem possa

expressar procedimentos paralelos, ela ainda precisa prover outras abstrações necessárias para modelar com precisão componentes de hardware.

Todo componente eletrônico tem atrasos de comunicação decorrentes da velocidade e de efeitos causados pelo movimento dos elétrons. Já citamos o campo magnético, crosstalking, dissipação de calor, variação na resistência entre outros. Cada um desses efeitos afeta de uma maneira ou de outra o tempo gasto no acionamento dos transistores constituintes das portas lógicas e consequentemente gerando atrasos nos sinais lógicos. Modelar esses atrasos é cada vez mais crítico dados os crescentes tamanho e complexidade dos sistemas modernos.

Além de permitir que os atrasos sejam modelados, as estruturas simples como fios e barramentos, curto-circuito e direção do sinal precisam também estar disponíveis para o projetista. Existem várias adaptações de linguagens de programação, utilizadas comumente apenas para geração de código executável para microprocessadores de uso geral, que implementam mecanismos adequados à descrição e implementação de componentes digitais. Esses mecanismos viabilizam a expressão de construções paralelas e entre essas linguagens podemos citar HandelC, VHDL, Verilog, System-Verilog e SystemC. Em cada uma dessas linguagens temos simuladores disponíveis que traduzem as indicações de atraso, mudança de valores e direção dos sinais em informações úteis que permitirão ao projetista decidir se o funcionamento do sistema é correto ou não e noções de como construir e integrar o sistema final.

Entre as diversas linguagens que podem ser utilizadas para a descrição de sistemas digitais, serão comparadas SystemC e VHDL. Para tanto, é necessário apresentar algumas informações preliminares sobre o SystemC.

## 1.3 SystemC

SystemC é uma biblioteca construída sobre o C++. C++ em seu início era também implementado através de estruturas da linguagem C que suportavam abstrações típicas das linguagens orientadas a objeto. No presente C++ tornou-se uma linguagem própria, mas mantendo compatibilidade com o legado do C. Um compilador C++ pode compilar um código C, mas a recíproca não é verdadeira. Os compiladores C já puderam compilar código C++ em seus primeiros estágios, entretanto, com a evolução da linguagem, isso não é mais verdadeiro. Tanto C como C++ podem utilizar bibliotecas escritas em uma ou outra linguagem desde que sejam fornecidas interfaces adequadas à linguagem C, além

da sintaxe dos operadores, comandos e funções comuns. Dessa forma, o SystemC é uma biblioteca com interface para o C++ e que implementa construções sem as quais seria muito trabalhoso descrever qualquer peça de hardware. Pode-se até questionar porque não usar C++, ou outra linguagem qualquer, diretamente, mas essa discussão remete a um problema semelhante a reinvenção da roda. É possível usar apenas C++ para implementar hardware, mas o esforço de modelagem é maior e certamente se sobrepõe a recursos já implementados, testados e documentados disponíveis no SystemC.

A base do SystemC é um núcleo de simulação dirigido por eventos. Esse núcleo reage aos eventos e faz a troca das tarefas para execução. O simulador é incapaz de diferenciar as finalidades das tarefas tratando-as de forma genérica. Os demais elementos do SystemC são portas (de entrada e saída, por exemplo), módulos para representar estruturas (que descrevem desde portas lógicas a procedimentos de alto nível, na forma de SC\_METHODs e SC\_THREADs), interfaces (assinaturas que serão utilizadas por outros módulos ou canais) e canais (sc\_fifo, sc\_mutex, sc\_signal, etc) que provêem a abstração de comunicação. O simulador, as portas, módulos, interfaces e canais formam o núcleo da linguagem. Junto ao núcleo ainda existem tipos de dados definidos na biblioteca do SystemC para bits, vetores de bits, inteiros de precisão arbitrária e outros tipos. Além de alguns tipos comuns às linguagens de descrição de hardware ainda é possível definir tipos personalizados usando a sintaxe adequada no C++.

Sobre o núcleo do SystemC estão descritos canais de uso comum como filas, sinais, temporizadores, *mutexes*, semáforos e outros. Com esses recursos é possível ampliar as funcionalidades do SystemC descrevendo, por exemplo, canais novos como barramentos variados e com diferentes opções de arbitragem.

Para estender o SystemC, usa-se módulos. Cada módulo é um bloco que esconde detalhes de implementação facilitando o processo de manutenção do sistema. Os módulos comunicam-se por portas bem definidas de entrada, saída ou de entrada e saída, e internamente possuem vários processos (ou métodos, no jargão das linguagens orientadas a objeto) que se comunicam por canais que podem ser primitivos do tipo requisição e atualização, como sc\_signal e sc\_fifo ou hierárquicos, que possuem estados internos e funcionamento complexo que pode usar árbitros, gerar múltiplos eventos e tratar erros, por exemplo. Além das portas, possuem tipicamente variáveis internas que funcionam como registradores do estado do sistema. Em um módulo é possível também usar outros módulos em hierarquia.

Ainda sobre módulos é necessário enfatizar que os processos são implementados como

métodos C++ e que no construtor se indica o tipo de processo, se método (SC\_METHOD) ou linha de execução (SC\_THREAD). A partir deste ponto, é necessário deixar claro que métodos se referem a métodos do SystemC, sobrepondo-se a terminologia das linguagens orientadas a objeto. Isto porque métodos do C++ sozinhos não apontam diferenças importantes na semântica de simulação, isto é, um método (SC\_METHOD do SystemC) pode possuir uma lista de sensitividade, ou seja, um conjunto de sinais que dispara sua execução sempre que qualquer um deles é modificado, atribuindo o comportamento de processo a funções. Observe-se que se um SC\_METHOD não termina, logo não executando completamente, o simulador não chega num estado estável e não prossegue. Já um processo tipo linha de execução (SC\_THREAD, ou simplesmente, thread) está sempre em execução sincronizada com o simulador, no sentido de que é possível inserir atrasos explícitos (através da função wait()) que instruem o simulador a avançar, interrompendo a thread e permitindo a execução de outros métodos e threads, viabilizando a descrição de componentes que demoram vários ciclos de relógio para executar. Modelar o comportamento multi-ciclo usando um método é mais complexo quando comparado a facilidade proporcionada por uma thread.

Através das SC\_THREADS é possível inserir atrasos medidos em tempo de relógio wall clock time no tempo do simulador diretamente no código. Esse comportamento não é sintetizável mas traz um grande poder de expressão à linguagem. Embora threads apresentem essa facilidade e executem sem interrupção entre funções wait() do SystemC, não é uma construção sintetizável. As construções sintetizáveis são usadas por ferramentas automáticas de síntese responsáveis por gerar a descrição da implementação física do hardware correspondente ao modelo. Métodos, quando marcados para execução serão acionados durante a simulação via chamada de função (como request e request\_update). O uso de uma estratégia distribuída, para executar métodos, isto é, vários processos do simulador, agrega ao tempo de simulação toda a sobrecarga associada a trocas de contexto e tempo de comunicação.

Ressalta-se também que o desempenho do simulador depende não apenas da linguagem, mas do suporte oferecido pela microarquitetura que executa o simulador.

As threads do SystemC executam do início ao fim e morrem quando sua execução termina por definição, não podendo ser reexecutadas após isso. Assim, se as threads não forem corretamente codificadas é possível que monopolizem o simulador, que não é preemptivo, comprometendo a simulação. Uma forma de resolver esta questão é introduzindo chamadas a função wait() do SystemC que permite que a thread seja escalonada, seja

para um instante de tempo determinado no futuro ou até que um determinado evento ou conjunto de eventos alternativos ou concorrentes ocorra.

A simulação no SystemC é baseada em eventos de diferentes tipos de acordo com o tipo de canal utilizado. Canais como FIFOs podem ter eventos como leitura, escrita e fila cheia. Canais do tipo sinal têm outros eventos como borda de subida, borda de descida, sinal em zero, sinal em um ou em estado indeterminado. Alguns objetos provêem eventos periódicos como o relógio (sc\_clock) que dita uma cadência de eventos dentro do sistema. Os eventos é que determinam se um dado método ou thread será marcado como pronto para ser executado ou não. Uma vez algo esteja pronto para execução o simulador poderá executá-lo ou continuar uma execução suspensa anteriormente (via wait(), por exemplo).

Quando os canais são especificados utiliza-se chamadas a função notify() para que a fila de execução do simulador possa ser preenchida. A execução a partir dos eventos pode ser [7] imediata, atraso delta (delta-delay) ou de atraso não zero (non zero delay). Notificações imediatas sempre vão determinar que os processos que dependem dela sejam acionados antes das atualizações dos canais primitivos. Notificações com atraso delta colocarão os processos em execução após a etapa de atualização dos canais primitivos, isto é, verão todas as modificações feitas nos canais primitivos. É importante visualizar que notificações imediatas são entregues antes que os valores novos dos canais primitivos sejam visíveis. Por fim, atrasos não zero são elencados em uma lista de eventos ordenada no tempo. Quando o simulador chega ao instante correto o evento é disparado.

Os eventos que colocam um método ou thread a disposição para execução podem ser estáticos ou dinâmicos. Os eventos estáticos estão definidos já antes de se iniciar a simulação. Os eventos dinâmicos suspendem a lista de definição dos eventos estáticos e forçam um processo a esperar por um evento específico.

Os canais básicos e os módulos, que interagem como colocado anteriormente via eventos e notificações, são utilizados por instanciação, isto é, são declarados e inicializados com nomes e características que os tornam únicos e reaproveitáveis em módulos mais complexos. O simulador, em tempo de execução, verifica as ligações entre as instâncias de cada canal e módulo declaradas e então procede com a simulação. Assim, é possível construir módulos e nesses módulos instanciam-se outros módulos a fim de montar o sistema final. Um processador por exemplo, é um módulo composto por outros módulos menores que funcionam de acordo com um relógio e estão integrados no seu núcleo.

Para concluir a exposição do SystemC, é necessário esclarecer como funciona a avalia-

ção dos eventos. Um ciclo-delta (ou delta-cycle) é uma porção infinitesimal de tempo que permite ordenar os eventos no simulador. Embora um evento seja avaliado em um ciclo delta, o tempo de simulação não avança e essa avaliação ainda é feita em dois passos que são avaliação e atualização, permitindo que a semântica associada aos canais primitivos (como tempo de propagação de um sinal) seja corretamente reproduzida.

Abaixo citamos o funcionamento do escalonador do SystemC a partir de [7]:

- Inicialização: cada processo é executado uma vez para SC\_METHODs ou até um ponto de sincronização (wait()) para os SC\_THREADs;

- 2. Avaliação: seleciona os processos que estão prontos para execução ou prontos para continuar, possivelmente executando notificações imediatas, com custo de ciclo-delta mas com atraso-zero (zero delay). Se as notificações imediatas forem mal utilizadas a simulação pode não sair deste ponto pois a avaliação se dá até que não existam mais processos prontos para continuar. Neste ponto são feitos pedidos de atualização;

- 3. Atualização: Os pedidos de atualização são executados até que não tenha mais pedido algum. Apenas o último pedido de atualização tem efeito caso tenha sido feito mais de uma vez para um mesmo canal;

- Se há notificações agendadas para o tempo atual de simulação (delta delay), determinar que processos estão aguardando e voltar a etapa de avaliação;

- 5. Se não há mais notificações agendadas para qualquer instante, o simulador termina;

- Se há outras notificações para o futuro, avança-se o tempo no simulador para o próximo instante, que é o da notificação agendada para mais cedo;

- 7. Determinar os processos que estão prontos para execução por eventos que tenham notificações pendentes no tempo atual e repetir a partir do estágio de Avaliação.

Para se comparar as duas linguagens, visualize o VHDL, e mesmo o Verilog, como uma linguagem desenvolvida especificamente para descrever sistemas digitais com um simulador semelhante ao do SystemC. Construções como fios, atrasos, atribuições paralelas e métodos paralelos são fáceis de representar nessas linguagens, entretanto, utilizar qualquer coisa fora do domínio dos modelos do hardware sendo projetado é difícil e compromete a execução do simulador. Gerar saída no console do simulador, fazer com que essa saída seja oriunda das respostas do sistema e realimentá-la é tarefa complexa. Por

exemplo, transformar informações matematicamente exige, no VHDL, um pacote matemático específico e a ausência desse pacote pode proibir a execução da simulação por falta de resultado. Mas o pacote matemático é um requisito que pode não ser necessário no sistema final pois uma tabela com os valores resolveria. Como o projetista perdeu recursos para prover o pacote matemático e apenas posteriormente descobriu uma solução barata, seu concorrente resolveu adotar SystemC e utilizar o processador matemático da CPU que executava o simulador, o que ele não conseguia fazer usando Verilog.

Da mesma maneira que o processador matemático da plataforma utilizada para executar o simulador VHDL não pode ser utilizado, os outros recursos computacionais como a interface de rede, o monitor de vídeo e outros dispositivos de entrada e saída também. Não há pacotes de fácil acesso que viabilizem tal coisa, mas, usando o SystemC e as interfaces disponíveis no ambiente pode-se utilizar todos os recursos disponíveis na plataforma do simulador de forma independente do SystemC ou do compilador C++ empregado utilizando bibliotecas de acesso do sistema operacional e dos dispositivos que são comumente escritos em C e tem amplo suporte da comunidade via Internet.

Visto que SystemC suporta estruturas que permitem modelar sistemas de hardware e que possui suporte para bibliotecas do sistema operacional e outras via bibliotecas do C, propõe-se que é possível integrar instâncias diferentes do simulador em máquinas diferentes como um sistema distribuído. Além de instâncias diferentes é possível encapsular outros sistemas e viabilizar a geração de eventos destes de forma visível ao simulador enriquecendo a experiência de simulação e diminuindo o tempo de implementação dos componentes do sistema final. Conforme expusemos, o simulador do SystemC não prevê que eventos gerados por outro simulador, ou programa ou hardware externo, executando em paralelo sejam levados em consideração durante a simulação, entretanto, é possível, através dos módulos adequados, expor os eventos gerados por um canal de comunicação em um simulador A e aguardar por estes eventos em um outro processo em um simulador B.

Uma vez implementado um canal de comunicação entre simuladores paralelos podemos distribuir o esforço computacional entre nós diferentes possivelmente aumentando a eficiência do sistema, seja otimizando a execução, seja usando recursos que de outra forma não estariam disponíveis. Neste trabalho focamos no segundo caso. Apresentaremos um módulo externo ao simulador que funciona de forma independente mas que consegue gerar eventos que se tornam compreensíveis para o simulador do SystemC.

Usando essa abordagem é possível diminuir o tempo necessário para se ter as primeiras

impressões do sistema funcionando visto que todos os recursos para a plataforma do simulador podem estar prontos, são encapsuláveis (como a rede e outros dispositivos de entrada e saída) e vão permitir um diagnóstico precoce dos elementos a otimizar, gargalos e custos diversos.

Outro uso prático do canal de comunicação entre simuladores paralelos seria sobrepor a execução de dois simuladores arranjados para execução de verificação funcional. No cenário indicado em [1] é apresentada uma bancada de testes com auto-verificação baseada em um modelo de referência. A dificuldade de executar dois simuladores paralelos, ou mesmo a complexidade de se integrar o modelo de referência e o dispositivo sendo testado no mesmo simulador são postos como dificultades. Tendo um canal de comunicação eficiente, capaz de gerar eventos e notificações entre os simuladores pode-se paralelizar a execução da verificação funcional, integrando suas diversas etapas. Sem a comunicação entre simuladores, é necessário guardar os estímulos e as respostas do design em arquivos e em uma etapa seguinte de alimentar os estímulos no modelo de referência e comparar suas respostas com os resultados do arquivo de saída gerado na fase anterior, processos sem sobreposição alguma.

#### 1.4 Justificativa

Durante o desenvolvimento de um sistema em silício são importantes as diversas etapas de verificação e refinamento dos modelos. Ver o comportamento do sistema em campo ou ter o desempenho do sistema final durante as etapas de simulação e desenvolvimento pode trazer efeitos positivos sobre possíveis investimentos e ainda chamar a atenção de que é possível fazer e que um sistema é eficiente, além de viabilizar medidas concretas do esforço necessário para se ter o sistema final em funcionamento.

A verificação da funcionalidade do sistema em níveis abstratos é uma etapa fundamental no projeto de sistemas em silício. Quanto mais cedo for a deteção de erros de projeto menor será o custo de sua correção [1]. No caso de sistemas em silício, existe um custo extremamente alto na sua fabricação física. A descoberta de erros de projeto depois da implementação física incorre em custos extremamente altos. Um exemplo clássico disso é a falha no processador Pentium da Intel em 1994, que só foi corrigida depois da fabricação e distribuição do processador. O custo monetário foi enorme, sem levar em conta o prejuízo a imagem da empresa. Por esses motivo, um esforço muito grande é feito durante a concepção do sistema para que ele execute corretamente já na primeira rodada

de fabricação.

A motivação para montar um estudo de caso vem do projeto Namitec [9], especificamente do grupo de Desenvolvimento de um SoC reconfigurável, com sensores integrados e capacidade de comunicação sem fio. Nesse grupo existe uma proposta de utilizar um SoC reconfigurável no rastreamento de objetos em campo, entre SoCs para outras finalidades.

Para tentar demonstrar que é possível um sistema de rastreamento em desenvolvimento com comportamento de uma implementação final e expor seus problemas em estágio inicial, tenta-se aqui implementar um segmentador de imagens, primeiro passo na constituição desse tipo de sistema, que constitua uma plataforma básica para o desenvolvimento desse SoC de rastreamento. Para isso é necessário implementar uma interface de captura de imagens, uma de segmentação e uma que disponibilize o resultado dessa segmentação para análise.

Conforme vemos em [17], o problema da segmentação de imagens é um passo básico para diferentes processos no campo das aplicações de processamento de informações visuais como:

- compressão de imagens baseadas em objetos;

- reconhecimento e rastreamento de objetos em sistemas de transporte inteligentes;

- visão computacional (para robôs);

- descrição de conteúdo multimidia como componentes espaço temporais;

- detecção de movimento.

Dos algortimos propostos para a segmentação de imagens, pode-se classificá-los a grosso modo em:

- Temporais: diferenças entre imagens consecutivas ou entre uma imagem e o fundo, com a desvantagem anunciada de que não é adequado para aplicações que necessitem obter tanto informações de objetos parados quanto em movimento;

- Espaciais (active contour, snake, sobel), baseadas em:

- pixel;

- bordas;

- regiões;

- modelos.

- Espaço-temporais.

Algoritmos temporais dependem da existência de pelo menos duas imagens que possam ser usadas como referência para o processamento. Algoritmos espaciais baseados em pixels e bordas demandam etapas de deteção de bordas e segmentação, além de que utilizam operações dispendiosas computacionalmente como produtos de matrizes e gradientes, o que desrespeita a autonomia, muito limitada, dos sistemas sem fio. Por isso decidiu-se utilizar a detecção de segmentos espaciais porposta em [20] e [8]. Esse algoritmo apresenta vantagens como pouca sensibilidade a ruídos, independência entre as imagens, processamento de pixels em paralelo, processamento de imagens coloridas ou monocromáticas e alto desempenho a baixo custo computacional.

O texto da dissertação é estruturado como segue. No capítulo 2 é realizada uma revisão sobre o desenvolvimento de modelos em SystmeC. No capítulo 3 apresenta-se conceitos relacionados a simulação distribuída e descreve-se a solução adotada neste trabalho para paralelizar a simulação de descrições SystemC. No capítulo 4 descreve- se o estudo de caso utilizado para analisar a solução proposta. Finalmente, as conclusões deste trabalho são discutidas no capítulo 5.

# $2 \quad Modelagem \ em \ SystemC \ de \ sistemas \ em \ silício$

## 2.1 Caracterização dos modelos mais comuns

Quando se descreve um sistema em silício é comum, nas diversas linguagens que podem ser utilizadas, dar detalhamentos diferentes para as diversas partes deste sistema. Existem algumas nomenclaturas, sem convenção definitiva ainda, associadas a alguma característica específica daquele nível de detalhamento. Quanto mais funcionalidade e menos detalhes de implementação o modelo expressa, diz-se que o modelo é de mais alto nível. Um modelo que tenha todos os detalhes possíveis é chamado um modelo de baixo nível. Pode ficar a sensação de que um modelo de baixo nível é ruim, entretanto, o modelo utilizado para a fabricação final do sistema é gerado com o auxílio de ferramentas de síntese é o modelo mais próximo da implementação final (física). A fabricação a partir de um modelo de alto nível sem restrições na codificação ainda não é possível pois não contempla muitos detalhes que a tecnologia contemporânea para implementação em silício requer.

Como existem diversas nomenclaturas para os níveis de descrição de hardware, descreve-se a utilizada neste trabalho a seguir. Uma especificação executável é o modelo de mais alto nível que consideraremos. Nele, não há qualquer referência a temporização, módulos ou modelo de comunicação, apenas é possível validar as entradas e as saídas do sistema como um todo, uma caixa preta responsável por abstrair todos os detalhes de implementação e decisões de projeto associadas. A especificação executável é de interesse de validação funcional e para futura depuração do sistema final. Ela pode ser apenas um oráculo com todas as respostas codificadas sem que as respostas sejam geradas por algoritmos e usada como base de comparação para as respostas produzidas através de decisões algorítmicas tomadas sobre as entradas dos modelos menos abstratos.

Considerando um desenvolvimento incremental, a partir da especificação executável

pode-se dar detalhes em diferentes níveis às partes do sistema. Cada detalhamento pode ser agrupado nas características: comunicação entre módulos, tempo de relógio (wall clock time), precisão de interfaces de comunicação em termos de pinos, precisão da execução em ciclos de relógio e precisão temporal nos atrasos dos sinais da implementação do sistema. O detalhamento da comunicação entre módulos pode ser feito de diversas maneiras, entre elas cita-se variáveis, métodos, funções, sinais, pinos ou portas e procedimentos. A comunicação por variáveis compartilhadas é uma das formas mais rudimentares que se pode usar para comunicar módulos distintos. Métodos, funções e procedimentos com suas respectivas assinaturas (que nada mais são que listas de parâmetros) podem agrupar funcionalidades que posteriormente podem ser implementadas como partes de software ou componentes de hardware com parâmetros bem definidos; através deles módulos diferentes podem usar e disponibilizar funcionalidades entre si. Sinais são utilizados para comunicar módulos com uma semântica de atualização definida (requisição de atualização e atualização efetiva), ou seja, mais elaborada que a atualização imediata característica das variáveis compartilhadas. Pinos são fronteiras de ligação típicas de módulos de hardware, podendo ser de entrada e/ou saída explicitando a direção da comunicação.

Uma vez que uma especificação apresente o detalhamento de comunicação entre seus módulos (módulos abstratos ou não) ela deixa de ser uma especificação funcional típica e pode ser detalhada como um modelo em nível de transações ou TLM de transaction level model. Esse modelo tem em si o detalhamento suficiente das informações trocadas entre os módulos do sistema, além da delimitação desses módulos (SC\_MODULE). Essa separação e definição das fronteiras de comunicação, mesmo que em nível abstrato permite que o modelo seguinte, ou modelo funcional temporizado, possa evidenciar o tempo de simulação. Não faremos distinção entre o modelo funcional não temporizado e o modelo TLM, como feito em [7].

Um modelo TLM tem como característica o foco nos problemas da aplicação como um sistema que pode ser implementado em hardware. Como resolver o problema deve ser tratado na especificação executável, por exemplo. Idealmente um modelo TLM é assíncrono, ou seja, para cada intervalo de tempo do simulador uma operação tem todos os dados que precisa para avançar e gerar uma resposta. Cada transação é auto contida, assim, uma transação n+1 não deve depender das entradas da transação n. Embora pareça com um modelo dataflow, uma transação pode interferir no tratamento de outra transação seguinte, mas não pode depender disso. Um exemplo é uma transação de transmissão de um dado. Se há necessidade de handshake ele deve estar na mesma transação que o dado de outra forma não seria transmitido por violação de protocolo. Esse mesmo dado

pode ainda instruir o canal a atrasar mensagens posteriores. É possível também que uma transação grande possua diversas transações menores, tantas quantas forem necessárias à funcionalidade. Cita-se como exemplo o barramento USB que precisa de várias mensagens com sincronização e sinalização de final, que podem ser encapsuladas em transações, com a finalidade de comunicar dados sendo que a seqüência das mensagens altera estados internos do sistema não necessariamente transmitindo o dado na primeira mensagem.

Num simulador de sistema de hardware, é importante ter em mente que temos três divisões temporais: o tempo de execução, o tempo de simulação (tempo do simulador) e o tempo do ciclo. Cada contador desses tempos avança de forma independente. O tempo de execução é medido pelo relógio cronológico (wall clock time) e varia em função da complexidade do sistema, do nível de detalhamento do modelo e dos recursos computacionais disponíveis. O tempo de simulação avança de acordo com a semântica do simulador e em intervalo definido durante a execução (pelo sc\_set\_time\_resolution ou na falta deste, no intervalo definido por sc\_clock para o SystemC, em outros simuladores o tempo avançará depois de processados todos os eventos gerados nos delta-delays). Não havendo eventos agendados para um instante dentro do intervalo do simulador, ele incrementará um tempo de ciclo. O tempo de ciclo dispara um evento regular recebido pelo sistema e que sincroniza sua execução. O modelo que leva em conta o tempo do simulador é o modelo funcional.

Através do modelo funcional é possível aumentar ou diminuir o tempo necessário para a emissão da resposta de cada módulo, no tempo do simulador, permitindo fazer testes de sincronização entre os módulos e fazer uma exploração do espaço de arquitetura e determinar limites relativos para os períodos de execução. No modelo TLM as funções do sistema são executadas conforme a disponibilidade dos dados. No modelo funcional, os atrasos codificados pelo programador interferem diretamente nessa disponibilidade.

A seguir, é necessário explicitar as fronteiras de comunicação do sistema em pinos de entrada e ou saída, que serão as interfaces com o exterior do circuito após a fabricação e que determinam os limites dos valores binários que podem ser comunicados e possivelmente sinais de controle. Uma descrição que tem todos os pinos correspondentes do circuito é chamado modelo comportamental ou behavioral model. Neste modelo o comportamento do sistema e seus módulos estão todos definidos com razoável precisão. Houve ferramentas de síntese (como foi o caso do behavioral compiler de [15]) que já conseguiram sintetizar o sistema físico final a partir de modelos comportamentais, desde que o código do modelo obedecesse a certas restrições e regras de codificação.

Para viabilizar uma síntese de melhor qualidade e mais eficiente, deve-se detalhar mais ainda o modelo do sistema, explicitando detalhes internos aos módulos e outros detalhes de comunicação. O modelo que detalha os módulos internamente é chamado de RTL, o register transfer level ou nível de transferência de registradores. Neste modelo o número de vezes que um módulo aparece no sistema e o seu compartilhamento ficam evidentes. Os protocolos de comunicação e multiplexação dos fios de comunicação devem ser bem definidos e geralmente obedecem orientações das ferramentas usadas para gerar automaticamente o modelo físico. Além disso, a temporização desse modelo é mais rigorosa e já não funciona apenas com a disponibilidade dos dados. Utiliza-se esse modelo para descrever circuitos síncronos, definido em termos de blocos de lógica combinacional e registradores. A transferência de informações é sincronizada por um relógio, e as tarefas tem duração definida em termos do número de ciclos de relógio.

Na especificação executável, no modelo TLM, no funcional e até mesmo no comportamental, a execução é orientada pela disponibilidade dos dados, caracterizando a execução como dataflow: o fluxo de dados determina um passo assíncrono para o sistema. Nos modelos RTL e GateLevel, a sincronização é feita pelo relógio do sistema. Os eventos são esperados e detalhados com base nos pulsos deste relógio e não mais com base na disponibilidade dos dados, o tempo não é mais dado de forma abstrata, representando um esforço maior por conta do codificador realizar qualquer modificação. Nesse nível de detalhamento, o número de ligações entre os componentes é maior e exige mais atenção no momento de acrescentar, remover, conectar e desconectar os pares de módulos.

No modelo físico, ou gate level, são descritos todos os transistores, fios e ligações entre os componentes eletrônicos do circuito. Esse modelo geralmente é feito automaticamente pelas ferramentas de síntese a partir de modelos RTL e comportamentais e demandam o máximo de esforço de implementação pois devem considerar a posição física de cada parte do sistema e os atrasos e efeitos das demais partes do sistema sobre si mesmo.

A tabela a seguir resume as principais diferenças e características dos modelos apresentados. Veja que deve ficar claro que os modelos de baixo nível têm necessariamente as características funcionais dos modelos de alto nível sempre com um detalhamento maior.

Em [3], vemos que são colocados apenas três níveis de detalhamento: comportamental, arquitetural e implementação. Isso é um leve contraste com [7] que apresenta os *modelos* em que nos baseamos. Assim, o nível comportamental compreenderia qualquer modelo sem informação de tempo (a especificação executável e o TLM). Para o nível arquitetural são separados os componentes que computam e os componentes que armazenam resulta-

|                     |           |         |              |           |            | Especif.      |

|---------------------|-----------|---------|--------------|-----------|------------|---------------|

|                     | GateLevel | RTL     | Behavioral   | FM        | TLM        | Executável    |

| Esforço             |           |         |              |           |            |               |

| de codificação      | ←         | Maior   |              |           | Menor      | $\rightarrow$ |

| Precisão de atrasos | X         | -       | _            | -         | =          | =             |

| Precisão de ciclos  | X         | X       | -            | -         | -          | -             |

| Precisão de pinos   | X         | X       | X            | -         | -          | -             |

| Tempo               | X         | X       | X            | X         | -          | -             |

| Comunicação         | X         | X       | X            | X         | X          | -             |

| Funcionalidade      | X         | X       | X            | X         | X          | X             |

| Sincronização       | precisa   | relógio | dataflow     | dataflow  | dataflow   | dataflow      |

| Comunicação         | sinais    | sinais  | sinais/filas | filas     | interfaces | (*)           |

| Tempo de simulação  | ←         | Maior   |              |           | Menor      | $\rightarrow$ |

| Foco nos tempos de  | atraso    | ciclo   | simulador    | simulador | execução   | execução      |

Tabela 1: Tabela comparativa dos modelos de descrição de hardware (\*) variáveis compartilhadas, métodos ou funções

dos, além dos fios, barramentos, portas de entrada e saída e informação abstrata de tempo (compreendendo o modelo funcional e comportamental). Para o nível de implementação, os componentes que computam resultados são descritos em termos de transferências de informações entre seus componentes por ciclo de relógio ou em termos de seqüências de instruções.

## 2.2 Implementação de alguns modelos em SystemC

Nesta seção apresentamos exemplos que caracterizam alguns modelos de interesse.

Uma especificação executável de uma ULA, unidade lógico aritmética, com 5 operações: multiplicar, dividir, somar, "e" lógico e "não" lógico, com indicação de erro para divisão por zero e sem *overflows* ou *underflows* pode ser da seguinte maneira:

```

// Definicoes comuns

#include <stdio.h>

#define _MUL 0

#define _DIV 1

#define _ADD 2

#define _oAND 3

#define _NOT 4

int ula(int a, int b, int op, int *err) {

```

```

int r = 0;

*err = 0;

switch(op) {

case _{MUL}: r = a * b; break;

case _DIV: if(b == 0) *err = 1; else r = a / b; break;

case _ADD: r = a + b; break;

case _oAND: r = a & b; break;

case _NOT: r = !a; break;

}

return r;

}

int main(int argc, char* argv[]) {

// Parse de parametros

int err, a, b, op;

if(argc < 3) return 0;

op = argv[1][0]-'0';

a = argv[2][0]-'0';

b = argv[3][0]-'0';

printf("Op: %u A: %u B: %u \n", op, a, b );

//

printf("Resultado: %u", ula( a, b, op, &err ) );

printf("Erro: %u \n ", err);

return 1;

}

```

Observe que nos modelos de especificação executável, a computação ocorre ainda de forma seqüencial, sem indicação do tempo gasto pelas operações e que basta um compilador C para que funcionem. Refinando o modelo percebe-se que o resultado da ULA estava implícito na chamada de função e temos então a noção exata dos valores que podem ser comunicados pela ULA.

```

//Definicoes comuns

...

typedef struct ula_t {

int err;

```

```

int a;

int b;

int op;

int r;

} ula_dummy;

void ula(struct ula_t *v_ula) {

v_ula->err = 0;

switch(v_ula->op) {

case _MUL: v_ula->r = v_ula->a * v_ula->b; break;

case _DIV:

if(v_ula->b == 0) v_ula->err = 1;

else v_ula->r = v_ula->a / v_ula->b; break;

case _ADD: v_ula->r = v_ula->a + v_ula->b; break;

case _oAND: v_ula->r = v_ula->a & v_ula->b; break;

case _NOT: v_ula - r = !(v_ula - a);

}

}

int main(int argc, char* argv[]) {

int err, a, b, op;

// Parse de parametros

. . .

//

struct ula_t ula_s;

ula_s.err=0;

ula_s.a=a;

ula_s.b=b;

ula_s.op=op;

ula( &ula_s );

printf("Resultado: %u", ula_s.r );

printf("Erro: %u \n ", ula_s.err);

return 1;

}

```

De acordo com os documentos do consórcio do SystemC [16], num modelo TLM toda comunicação deve ser feita via chamada de funções. Assim, precisamos modificar nova-

mente a ULA para que ela receba e devolva seus operadores através de funções padronizadas e passe então a efetivamente requerer o SystemC. Quando da escrita desse documento a função padrão utilizada para os modelos TLM tem semântica de interface idêntica à da classe sc\_fifo, a qual utilizaremos por nos parecer de mais fácil compreensão, sem entrar no mérito da implementação da interface.

```

// Definicoes comuns

#include "systemc.h"

#include <stdlib.h>

typedef struct ula_ti {

int a;

int b;

int op;

} ula_dummyi;

typedef struct ula_to {

int err;

int r;

} ula_dummyo;

SC_MODULE(ula) {

sc_fifo_in <struct ula_ti *> inputs;

sc_fifo_out<struct ula_to *> outputs;

void operate(void) {

struct ula_to r;

struct ula_ti *vi_ula;

while(true) {

vi_ula = inputs.read();

r.err = 0;

switch(vi_ula->op) {

case _MUL: r.r = vi_ula->a * vi_ula->b; break;

case _DIV: if(vi_ula->b == 0) r.err = 1;

else r.r = vi_ula->a / vi_ula->b; break;

case _ADD: r.r = vi_ula->a + vi_ula->b; break;

case _oAND: r.r = vi_ula->a & vi_ula->b; break;

```

```

case _NOT: r.r = !(vi_ula->a); break;

}

outputs.write(&r);

}

}

SC_CTOR(ula) {

SC_THREAD(operate);

}

};

int sc_main(int argc, char* argv[]) {

// Parse de parametros

//

ula sc_ula("sc_ula"); // Instanciar a ula;

sc_fifo <struct ula_ti *> ula_si; // // Instanciar canal

sc_fifo <struct ula_to *> ula_so; // // Instanciar canal

struct ula_ti ula_vi; // Valores

struct ula_to *ula_vo; // Valores

sc_ula.inputs(ula_si); // Ligacoes

sc_ula.outputs(ula_so);

// Valores de entrada

ula_vi.a=a;

ula_vi.b=b;

ula_vi.op=op;

ula_si.write(&ula_vi);

// Simulacao

cout << "Ready to start!"<< endl;</pre>

sc_start(2);

cout << "Simulation is over!" << endl;</pre>

// Valores de saida

ula_vo = ula_so.read();

printf("Resultado: %u ", ula_vo->r );

printf("Erro: %u \n ", ula_vo->err);

```

```

return 1;

};

```

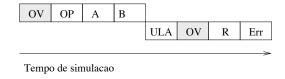

O último modelo que apresentaremos exemplo é o funcional temporizado. Neste modelo, as diferentes operações levam tempos diferentes para concluir. Esse tempo diferente é estimado e colocado na função wait() para permitir expressar o custo computacional, e conseqüentemente explorar o espaço de arquitetura. Para tanto, exibimos a seguir os trechos de código modificados:

```

. . .

switch(vi_ula->op) {

case _MUL:

r.r = vi_ula->a * vi_ula->b; wait(45, SC_NS); break;

case _DIV:

if(vi_ula->b == 0) r.err = 1;

else r.r = vi_ula->a / vi_ula->b; wait(35, SC_NS); break;

case _ADD:

r.r = vi_ula->a + vi_ula->b; wait(10, SC_NS); break;

case _oAND:

r.r = vi_ula->a & vi_ula->b; wait(10, SC_NS); break;

case _NOT: r.r = !(vi_ula->a); wait(5, SC_NS); break;

}

outputs.write(&r);

cout << "Tempo do simulador " << sc_time_stamp() << endl;</pre>

int sc_main(int argc, char* argv[]) {

// Parse de parametros

. . .

//

sc_set_time_resolution(1.0, SC_NS);

ula sc_ula("sc_ula"); // Instanciar a ula;

// Simulacao

cout << "Ready to start!"<< endl;</pre>

sc_start(10); cout << "10 ns" << endl;</pre>

```

sc\_start(10); cout << "20 ns" << endl;

```

sc_start(10); cout << "30 ns" << endl;

sc_start(10); cout << "40 ns" << endl;

sc_start(10); cout << "50 ns" << endl;

cout << "Simulation is over!" << endl;</pre>

```

Ao executarmos o modelo com as modificações propostas temos os resultados a seguir:

| Parâmetros      | t0     | t1     | t2     | t3     | t4                 | t5     | Resultado | Erro |

|-----------------|--------|--------|--------|--------|--------------------|--------|-----------|------|

| Op: 0 A: 5 B: 5 | 10 ns  | 20 ns  | 30 ns  | 40 ns  | 45  ns             | 50 ns  | 25        | 0    |

| Op: 1 A: 5 B: 0 | 10  ns | 20  ns | 30  ns | 35  ns | $40 \mathrm{\ ns}$ | 50  ns | 0         | 1    |

| Op: 2 A: 5 B: 3 | 10  ns | 10  ns | 20  ns | 30  ns | 40  ns             | 50  ns | 8         | 0    |

| Op: 4 A: 5 B: 3 | 5  ns  | 10  ns | 20  ns | 30  ns | 40  ns             | 50  ns | 0         | 0    |

Tabela 2: Resultados do modelo funcional temporizado

Observe os tempos abordados anteriormente. O tempo de execução do código é muito curto, praticamente instantâneo. O tempo do simulador avança em passos irregulares dados pelos atrasos da ULA e o tempo de ciclo é de 10ns, e avança de forma manual. Para gerar um relógio com pulsos de comprimento 20 ns bastaria adicionar um sinal e mudar o seu valor entre cada sc\_start(10), mas é possível gerar eventos periódicos usando uma linha de relógio sc\_clock do SystemC produzindo eventos periódicos automaticamente e executar o simulador por tempo indefinido, chamando-se sc\_clock() sem parâmetros.

Os demais modelos não serão apresentados pois entram em detalhes como número de bits das entradas e saídas e a propagação da linha com o relógio (clock) e fogem do escopo deste trabalho. Nos modelos apresentados, a comunicação é feita de forma explícita mas não detalhada em grânulo fino: não é possível dizer quantos ciclos de relógio são necessários para multiplicar ou que algoritmo é usado nem quantos pinos teria um chip com a ULA implementada. No modelo TLM e no modelo funcional temporizado a idéia é estabelecer uma ordem de atualização dos sinais e verificar o seu comportamento em situação de concorrência e não determinar quantos ciclos exatos toma a execução de cada componente; essa tarefa está no nível do modelo RTL, após a definição da precisão dos tipos que estão sendo operados. Combinar ULAs como a descrita já responde questões sobre como o sistema final responderá caso a temporização das multiplicações em relação às somas não seja respeitada.

Cabe ainda dizer que no modelo TLM apresentado foi utilizada uma interface padrão do SystemC, a sc\_fifo. Entretanto, o poder de expressão dessa linguagem é bem maior. Através de event finders, events definidos pelo usuário e da chamada notify() é possível

definir canais complexos com diversas fases e estados internos com interações complexas ao longo do código ainda assim garantindo a reusabilidade. Detalhes sobre esse tipo de implementação podem ser encontrados em [7]. Para implementar o modelo proposto de simulação distribuída será mantido o uso do sc\_fifo por simplicidade.

Espera-se que com modelos abstrato escondendo detalhes particulares de sincronização entre os módulos através de interfaces diminua-se o ciclo de desenvolvimento e torne possível visualizar a execução de camadas superiores da aplicação sem que as camadas inferiores estejam completamente detalhadas. Definidas as funcionalidades, propomos diminuir o tempo de execução da simulação e viabilizá-la permitindo o uso de recursos de coexistência inviável com a biblioteca do SystemC.

## 3 Simulação distribuída

Ao modelar sistemas complexos, os recursos de um único computador podem não ser suficientes para gerar resultados em tempo hábil. Quanto mais detalhes modelados mais tempo o simulador levará executando um mesmo cenário. Nem todos os recursos necessários para a execução do sistema podem estar disponíveis em um mesmo nó. Para diminuir o impacto desses problemas em sistemas modelados em SystemC pode-se distribuir o simulador em diversas máquinas, num *cluster* heterogêneo. Para possibilitar essa distribuição, é necessário rever alguns conceitos e acompanhar alguns exemplos.

Num modelo TLM, mesmo com a descrição do hardware em estágio inicial, é possível que o custo de execução do sistema seja alto. Um exemplo disso é o modelo de verificação utilizado em projetos como o BrazilIP [2] [18] e citado em [1] como um possível arranjo para a verificação funcional. No caso do dispositivo USB, implementado pela Universidade de Brasília, foram gastas mais de 24 horas executando a simulação com uso de CPU em 100%. No caso do decodificador mpeg, implementado pela UFCG, um ganho razoável pôde ser observado quando comparada a execução da simulação em um computador de 32bits com um processador e um computador com dois processadores de 64 bits, utilizado para diminuir o tempo de simulação.

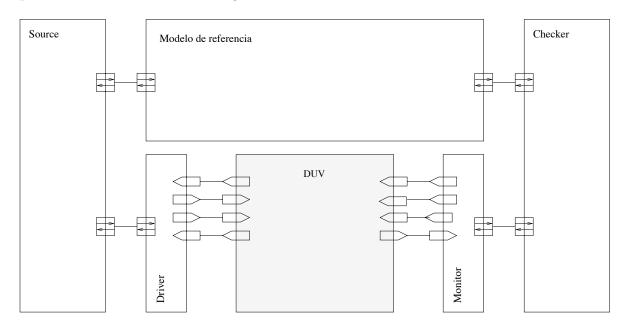

O modelo utilizado para fazer a verificação desses dispositivos consistia em utilizar um modelo TLM externo que fornecesse os estímulos idênticos (source) a um modelo de referência, preferencialmente uma especificação executável, e ao dispositivo sendo testado (Design Under Verification ou apenas DUV) e os resultados fornecidos para um comparador (checker) responsável por verificar se as respostas do modelo de referência são equivalentes às respostas do DUV. Os dispositivos sendo testados eram modelos RTL usados posteriormente como entrada para ferramentas de síntese automática. Para que as transações de alto nível pudessem ser traduzidas do source para o modelo RTL e de volta para o checker foram utilizados drivers responsáveis por implementar os protocolos de comunicação e injetar os sinais apropriadamente no DUV, e monitores, responsáveis por coletar os resultados e repassá-los ao checker. Veja a ilustração do modelo de verificação,

apelidado de "U invertido", na figura 1

Figura 1: Modelo do "U" invertido utilizado no BrazilIP

Os ganhos no tempo de simulação obtidos no caso do decodificador mpeg foram oriundos dos recursos disponibilizados pelo sistema operacional para o simulador do SystemC. O sistema operacional tinha a disposição dois processadores de melhor desempenho e arquitetura de 64bits podendo dividir os processos do simulador e do sistema operacional. Mesmo que os dois processadores não fossem utilizados pelo simulador os processos de responsabilidade do SO são executados em paralelo. Para criar uma visão única do sistema, disponibilizando os dois processadores para o simulador é necessário rever como o simulador do SystemC funciona.

No capítulo anterior citamos que o simulador do SystemC executa os SC\_METHODs seqüencialmente, com cada SC\_METHOD executando em tempo infinitesimal (um delta\_cycle) sem avançar o tempo do simulador, desde que eles estejam prontos para execução, comportamento que se repete para os SC\_THREADs até que seja encontrada alguma primitiva bloqueante ou wait(). As threads e métodos do SystemC (versão 2.0.1) são postos em execução através da framework QuickThreads [12], que é uma conjunto de funções e mecanismo de encapsulamento para implementar threads, ou seja, processos leves dentro de um processo do sistema operacional.

A vantagem de se utilizar uma thread é que o tempo extra gasto pelo sistema operacional para guardar e recuperar o contexto do processo é reduzido. No caso das quickthreads, elas não são preemptivas, ou seja, sempre vão executar até devolverem o controle ao processo principal, ou thread do escalonador. Uma pequena desvantagem da implementação do SystemC é que as threads executam sobre um único processo e depende do sistema operacional para que seja alocada em mais de um processador. Daí concluímos que se o sistema operacional não puder oferecer múltiplos processadores a um processo não poderemos obter ganhos em tempo de simulação para uma mesma arquitetura onde se possa variar o número de processadores.

Uma solução barata para forçar o uso de vários processadores poderia ser utilizar uma primitiva como "fork" e obter dois processos idênticos executando a simulação e comunicando-se usando algum mecanismo de IPC (interprocess communication). Ainda assim resta o problema de comunicar os simuladores em processadores funcionando em paralelo. Esse problema de comunicação quando resolvido permite, além de possivelmente tornar a execução mais rápida, que processos alheios ao simulador, como dispositivos de entrada e saída quaisquer, possam se comunicar com os dispositivos sendo simulados, ampliando as possibilidades da linguagem.

Computadores podem ser classificados usando a classificação de Flynn [6], em arquiteturas do tipo SISD (um fluxo de instruções e um fluxo de dados), SIMD (um fluxo de instruções e vários fluxos de dados), MISD (vários fluxos de instruções e um fluxo de dados) e MIMD (multiprocessador, vários fluxos de instruções e vários fluxos de dados). Arquiteturas SISD e SIMD são mais comuns e não oferecem paralelismo em nível de processos, isto é, processos paralelos. Arquiteturas MISD não possuem implementação representativa. As arquiteturas MIMD (multicomputadores, clusters ou Network of Workstations, várias CPUs ligadas por uma rede de alto desempenho, uma máquina paralela) são interessantes por permitir que um mesmo problema possa ser abordado por diferentes processadores em diferentes processos, sejam através de múltiplos programas ou de um mesmo programa executando em nós diferentes.

A implementação da comunicação entre os processadores, isto é, entre os processos que executam nesses processadores pode ser feita em diferentes níveis. Os diversos níveis que uma máquina paralela possui em sua arquitetura, são citados a seguir, do mais alto ao mais baixo [4]:

- Modelo de programação: esconde a ordem de execução atrás da ordem sequencial do programa;

- (a) Multiprogramação (CAD): não há coordenação ou comunicação entre as tarefas:

- (b) Endereçamento compartilhado (shared memory): todas as tarefas podem ver o

- que as outras tarefas concorrentes estão fazendo e tomar decisões;

- (c) Troca de mensagens (message passing): a comunicação é iniciada explicitamente entre os pontos envolvidos (por exemplo: sockets, pipes, sistemas de filas);

- (d) Dados paralelos (data parallel): os dados são processados ao mesmo tempo com um evento de sincronização a cada passo; as arquiteturas data parallel compreendem os processadores vetoriais, os vetores processadores e registradores vetoriais para Load e Store;

- (e) Dataflow: um pipeline circular simples que explora o casamento de *tokens* com as operações básicas de *tag match*, alocar *buffer*, transferir dados e postar eventos;

- (f) Sistólico: os dados se movem em um vetor de elementos processadores.

- Abstração de comunicação, limite entre o usuário e o sistema: estabelece um compromisso entre o software e o hardware de forma a trabalhar corretamente sem proibir a exploração tecnológica;

- (a) Software/Multiprogramação;

- (b) Bibliotecas (MPI, PVM);

- (c) Sistema operacional.

- 3. Hardware de comunicação;

- 4. Meio de comunicação.

O sistema operacional pode disponibilizar suporte do hardware do processador, fornecer opções de entrada e saída, o escalonador ou dispositivos de rede (para sistemas

multicomputadores). Quando se utiliza bibliotecas que expõem os recursos do sistema

operacional de forma padrão em diversas plataformas, diz-se que essas bibliotecas são

responsáveis por criar uma visão única do sistema em que o programador não precise se

preocupar com a distribuição dos processos e número de nós, por exemplo.

Dentro das camadas de abstração que apresentamos, nenhum dos mecanismos faz parte do SystemC. Iremos utilizar na camada mais alta troca de mensagens para comunicar os processos. Essa comunicação é implementada em nível de biblioteca do sistema operacional que abstrai o hardware e o meio de comunicação. Adotaremos troca de mensagens por ser de uso mais intuitivo. Os nós serão endereçados no início da execução e a

comunicação entre eles se dará por primitivas send e receive, principalmente para evitar problemas de concorrência com as escritas, leituras e semáforos associados ao modelo de memória compartilhada e por não haver disponibilidade de máquinas sistólicas, dataflow ou data parallel para esse estudo.

## 3.1 Processo de paralelização

O processo de paralelização envolve quatro etapas:

- 1. decomposição do cômputo em tarefas, expondo a concorrência

- 2. atribuição de tarefas aos processos, agrupamento de tarefas e balanceamento de carga

- 3. coordenação dos acessos a dados, comunicação, sincronização e redução de comunicação (escolha de primitivas bloqueantes, não bloqueantes ou síncronas)

- 4. delegação dos processos aos processadores, exploração do princípio da localidade (dados privados)

No processo de paralelização, questões importantes são levantadas e que geralmente interferem em maior ou menor proporção em diferentes etapas, uma vez que: no processo de coordenação certas tarefas podem ser atribuídas a outros processos; podem expor maior ou menor concorrência; ser estáticas ou dinâmicas; ter variado seu tamanho de grânulo e ainda há a questão do balanceamento de carga que incorre em lógica extra de gerenciamento, serialização e mesmo em custo de sincronização.

A atribuição de tarefas pode ser estática ou dinâmica, sendo que o dinamismo na atribuição de tarefas abre um leque de opções com vantagens bem peculiares. Algumas formas de atribuição de tarefas: semi-estática, fixada via *profiles*, tarefas dinâmicas, auto-escalonadas com ou sem guia, filas centralizadas ou distribuídas com ou sem roubo de tarefas (*task stealing*).

O balanceamento de carga pode fazer uso de diversos modelos conhecidos como o paralelismo de dados, o paralelismo de funções, controle, tarefas e a técnica de pipelines. Os efeitos colaterais da descentralização são a serialização e as opções de sincronização de desempenho, além de dificuldades de uso variadas como barreiras, sincronização ponto a ponto ou por grupos, bem como o uso de mecanismos de trava ou *locks*: individuais,

pequenos de seção crítica, semáforos ou grupos de travas em vetores ou tabelas de hash. Outras questões a resolver no balanceamento são a distribuição dos dados e do código e computações redundantes.

## 3.2 Aplicação do processo de paralelização

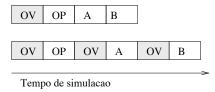

De acordo com o processo de paralelização colocado em [4] e citado na seção anterior, o cômputo precisa ser decomposto em tarefas, expondo a concorrência. Cada tarefa em um projeto SystemC pode ser expressa em diferentes níveis de detalhe. Utilizando o exemplo da ULA, podemos ver que transmitir uma transação inteira, com os operandos e o operador seria mais barato que transmitir separadamente cada operando e o operador separadamente, dada uma latência positiva e todo o overhead de comunicação. Veja a figura 2

Figura 2: Exemplo de acumulação do *overhead* de comunicação no tempo total de simulação

Deve-se visualizar que cada vez que um dado é comunicado e que se aguarda uma resposta agregamos ao tempo de execução duas vezes a latência de comunicação (figura 3). Assim, precisa-se levar em consideração o que se comunica em cada um dos modelos possíveis de se descrever na linguagem e quanto ele agrega em tempo final de simulação.

Figura 3: Exemplo de acumulação do overhead de comunicação bidirecional no tempo total de simulação

Conforme citamos no capítulo 2, os modelos gate level, RTL e comportamental apresentam os detalhes de comunicação em nível de pinos e logo não são candidatos à comunicação entre processos a menos que um conjunto de valores representados pelos pinos possa ser agrupado em uma transação passível de interpretação por um par driver/monitor imitando um modelo de mais alto nível. Modelos funcionais e TLM já tem um grão de

comunicação maior, bom candidato a ser transmitido para processamento em outro nó. A especificação executável, por sua natureza, pode ser paralelizada usando qualquer estratégia tradicional pois não tem compromisso com as fronteiras de comunicação da mesma forma que os modelos do sistema. A partir deste ponto os modelos funcionais e TLM serão referenciados apenas como TLM.

#### 3.2.0.1 Decomposição em tarefas