## DISSERTAÇÃO DE MESTRADO

## Implementação de um Classificador de Imagens Baseado em Redes Neurais em Sistemas Embarcados

Thiago Marques Siqueira

Brasília, Julho de 2016

## UNIVERSIDADE DE BRASÍLIA

FACULDADE DE TECNOLOGIA

## UNIVERSIDADE DE BRASÍLIA

Faculdade de Tecnologia

## DISSERTAÇÃO DE MESTRADO

## Implementação de um Classificador de Imagens Baseado em Redes Neurais em Sistemas Embarcados

#### Thiago Marques Siqueira

Dissertação submetida ao Departamento de Engenharia Mecânica da Faculdade de Tecnologia da Universidade de Brasília como requisito parcial para obtenção do grau de Mestre Engenheiro em Sistemas Mecatrônicos.

#### Banca Examinadora

| Prof. Dr. Ricardo Pezzoul Jacobi, ENM/UnB Orientador         |  |

|--------------------------------------------------------------|--|

| Prof. Dr. Carlos Humberto Llanos, ENM/UnB Examinador interno |  |

| Prof. Dr. Janier Arias, DELT/UFMG  Examinador externo        |  |

#### FICHA CATALOGRÁFICA

#### SIQUEIRA, THIAGO MARQUES

Implementação de um Classificador de Imagens Baseado em Redes Neurais em Sistemas Embarcados

[Distrito Federal] 2016.

xii, NP. 87, 210 x 297 mm (ENM/FT/UnB, Mestre, Sistemas Mecatrônicos, 2016).

Dissertação de Mestrado - Universidade de Brasília. Faculdade de Tecnologia.

Departamento de Engenharia Mecânica.

1. Sistemas Embarcados

2. Sistemas Reconfiguráveis

3. ARM & FPGA

4. HLS

I. ENM/FT/UnB

II. Título (série)

#### REFERÊNCIA BIBLIOGRÁFICA

SIQUEIRA, T.M. (2016). Implementação de um Classificador de Imagens Baseado em Redes Neurais em Sistemas Embarcados, Dissertação de Mestrado em Sistemas Mecatrônicos, Publicação ENM.DM-106/16, Departamento de Engenharia Mecânica, Faculdade de Tecnologia, Universidade de Brasília, Brasília, DF, NP. 87

#### CESSÃO DE DIREITOS

AUTOR: Thiago Marques Siqueira

TÍTULO: Implementação de um Classificador de Imagens Baseado em Redes Neurais em

Sistemas Embarcados.

GRAU: Mestre ANO: 2016

É concedida à Universidade de Brasília permissão para reproduzir cópias desta dissertação e para emprestar ou vender tais cópias somente para propósitos acadêmicos e científicos. O autor reserva outros direitos de publicação e nenhuma parte desse trabalho de conclusão de curso pode ser reproduzida sem autorização por escrito do autor.

Thiago Marques Siqueira

Brasília - DF - Brasil

|                                                                                   | Dedicatória             |

|-----------------------------------------------------------------------------------|-------------------------|

| Dedico essa dissertação a minha mãe que sempre me apoia nas mentos da minha vida. | s minhas decisões e mo- |

| I                                                                                 | Thiago Marques Siqueira |

|                                                                                   |                         |

|                                                                                   |                         |

|                                                                                   |                         |

|                                                                                   |                         |

#### Agradecimentos

Agradeço em especial a minha mãe, por acreditar em mim e ficar sempre ao meu lado nos momentos mais difíceis desse mestrado. Agradeço também ao meu professor orientador Dr. Ricardo Pezzoul Jacobi por me guiar e pela oportunidade de trabalho com o desenvolvimento de novas tecnologias. Sou grato também ao Dr. Emerson Lopes Machado, por fornecer o código fonte do xQuant e toda ajuda de forma detalhada para compreensão do algoritmo e ao Renato Sampaio pelo compartilhamento de informação a respeito design em FPGA.

Thiago Marques Siqueira

Durante décadas, classificadores baseados em rede neural feedforward (FNN, do inglês, feedforward neural network) têm sido amplamente utilizados em muitos problemas de classificação, como imagem [1] e reconhecimento de fala [2]. Porém esse descoberta veio com algumas desvantagens, o grande número de multiplicações em ponto flutuante necessário em tempo de teste e a quantidade de memória necessária para armazenar os parâmetros treinados. Isso ocorre porque a maioria dos seus cálculos são produto de matrizes por vetores, onde as imagens de entrada dispostas como vetores são multiplicados por uma matriz de parâmetros aprendida para um conjunto específico de imagens. Quando implementados em hardware dedicado, a principal vantagem de um classificador FNN sobre os outros classificadores é a sua natureza inerente de paralelizar as operações de multiplicação. No entanto, quando o número de parâmetros de um classificador FNN é grande, surge o desafio na alta quantidade de recursos necessários para implementar operações de multiplicação seguida de acumulação (MAC, do inglês multiply-accumulate operations) e a dificuldade de transferir os dados da memória para a unidade de processamento com uma baixa latência. Houve uma extensa pesquisa na literatura sobre estratégias de quantização para resolver esses problemas. Entre essas estratégias de quantização, o xQuant [3] quantiza os parâmetros do classificador FNN primeiramente reescalonando para valores inteiros e, em seguida, aproximandoos ao respectivo potência de 2 mais próximo. Quando um classificador quantizado com xQuant é utilizado para classificar imagens, cada multiplicação de ponto flutuante é substituído por uma única operação de deslocamento de bits. No entanto, xQuant ainda não foi implementado em um hardware dedicado.

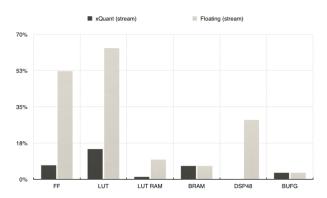

Portanto, nessa dissertação de mestrado é apresentado uma análise da implementação do xQuant em FPGA. Usando o algoritmo de aprendizagem classificador FNN LAST (Learning Algorithm for Soft-Thresholding), o classificador foi treinado para um problema de classificação de textura e utilizado este classificador como estudo de caso. Esse foi implementado como um coprocessador (Hardware / Software), uma arquitetura usando o ponto flutuante de precisão simples (Fp) e uma versão quantizada do classificador usando xQuant (xQ). Ambos os projetos foram implementados em um Xilinx Zynq-7020 SoC, utilizando a ferramenta Xilinx Vivado HLS. Os resultados mostram que xQ executa 3 vezes mais rápida do que Fp e o uso de recursos da FPGA como se segue: FF de 52% para 7%; LUTs de 63% para 15%; LUTRAMs de 10% para 1%; dispositivo de DSP de 29% para 0. Com essa redução de recursos é uma alternativa bem vista, para sistemas embarcados críticos, onde a quantidade de recursos e de energia disponíveis são limitados.

Palavras Chaves: Classificador FNN, quantização, xQuant, FPGA, HLS.

#### ABSTRACT

For decades, classifiers based on Feedforward Neural Network - FNN have been widely used in many classification problems, such as image [1] and recognition voice [2]. However this discovery came with some drawbacks, the number of multiplications necessary in floating point in test time and the amount of memory required to store the trained parameters. This it happens because the most of calculations are multiplications between matrices and vectors, where the input images arranged as vectors are multiplied by a parameter array learned for a specific set of images. When implemented in dedicated hardware, the main advantage of a FNN classifier on the other classifiers is their inherent nature to parallelize the multiplication operations. However, when the number of parameters of a FNN classifier is large, the challenge in high amount of resources needed to implement Multiply-Accumulate Operations - MAC and the difficulty of transferring data from memory to the processing unit with a low latency. There was an extensive literature search on quantization strategies to solve these problems. Among these quantization strategies, xQuant [3] first rescales them to integer values and then quantizes them by approaching each weight to its nearest power of two. When a quantized classifier xQuant is used to classify images, each floatingpoint multiplication is replaced by a single bit shift operation. However, xQuant has not yet been implemented in a dedicated hardware.

Therefore, in this master thesis is presented an analysis of the implementation of xQuant on FPGA. Using the classifier Learning Algorithm for Soft-Thresholding - FNN LAST, the classifier was trained to a texture classification problem and used this classifier as a case study. This was implemented as a coprocessor (Hardware / Software), an architecture using the floating-point single precision (Fp) and a quantized version of the classifier using xQuant (xQ). Both projects were implemented on Xilinx Zynq-7020 SoC, using the Xilinx Vivado HLS tool. The results show that performs xQ 3 times faster than Fp and use of FPGA resources as follows: FFs from 52% to 7%; LUTs from 63% to 15%; LUTRAMs from 10% to 1%; DSP slices from 29% to 0. With this reduction in resources is an alternative view and, for critical embedded systems where the amount of resources and energy are limited.

**Keywords**: FNN Classifier, quantization, xQuant, FPGA, HLS.

# **SUMÁRIO**

| 1 | Introd | ução                                                   | 1  |

|---|--------|--------------------------------------------------------|----|

|   | 1.1    | Contextualização                                       | 2  |

|   | 1.2    | Perguntas de Pesquisa                                  | 4  |

|   | 1.3    | Objetivo Geral                                         | 4  |

|   | 1.4    | Objetivo Específico                                    | 4  |

| 2 | Funda  | mentação Teórica                                       | 5  |

|   | 2.1    | Sistemas Embarcados                                    | 5  |

|   | 2.1.1  | Processadores ARM                                      | 6  |

|   | 2.1.2  | Field Programmable Gate Array - FPGA                   | 7  |

|   | 2.1.3  | System on Chip - SoC                                   | 10 |

|   | 2.1.4  | Comunicação entre ARM & FPGA                           | 13 |

|   | 2.2    | Classificador de Imagem com Arquitetura em Rede Neural | 15 |

|   | 2.2.1  | Conceito de Classificador                              | 16 |

|   | 2.2.2  | Learning Algorithm for Soft-Thresholding (LAST)        | 18 |

|   | 2.3    | Multiplicação Matriz-Matriz                            | 20 |

|   | 2.3.1  | Algoritmo Padrão                                       | 20 |

|   | 2.3.2  | Multiplicação em Bloco                                 | 20 |

|   | 2.3.3  | Algoritmo Strassen                                     | 21 |

|   | 2.4    | Aproximação para Potências de 2 mais Próximas (xQuant) | 22 |

| 3 | Imple  | mentação do Classificador LAST em um Sistema Embarcado | 24 |

|   | 3.1    | Bases de Dados Utilizadas                              | 24 |

|   | 3.2    | Implementação                                          | 25 |

|   | 3.3    | Implementação em Software                              | 26 |

|   | 3.4    | HIGH LEVEL SYNTHESIS - HLS                             | 27 |

|   | 3.5    | Implementação em FPGA Utilizando Floating Point        | 28 |

|   | 3.6    | Implementação em FPGA Utilizando xQuant                | 30 |

| 4 | Anális | e das Diferentes Implementações Realizadas             | 31 |

|   | 4.1    | Resultados e Discussões                                | 31 |

| 5 | Concl  | uções la Trabalhos Futuros                             | 27 |

| RE           | EFERÊI | NCI     | $\mathbf{AS}$ | • •   | • • • | • • | <br>• • | • • • | <br>• • | • • • | • •   | • • |       | • • | • • |     | • • | • • |       | • • | • • |     | • •   | • •   |       | • •       | • • • | 39        |

|--------------|--------|---------|---------------|-------|-------|-----|---------|-------|---------|-------|-------|-----|-------|-----|-----|-----|-----|-----|-------|-----|-----|-----|-------|-------|-------|-----------|-------|-----------|

| An           | exos   | • • • • | • • • •       |       |       |     | <br>    | ••    | <br>    |       | • • • |     |       |     |     | • • |     |     |       |     |     | • • | • • • | · • • |       |           |       | 42        |

| Ι            | Anexo  | 01.     | •••           | • • • | • •   |     | <br>    | • •   | <br>    | • • • |       |     | • • • |     |     |     | ••  | ••  |       |     | ••  |     | •••   |       |       | . <b></b> |       | 43        |

| II           | Anexo  | 02 .    | •••           | •••   | • •   |     | <br>    | • •   | <br>    | •••   |       |     | • •   |     |     |     |     | ••  |       |     | ••  |     | •••   |       |       | . <b></b> | • • • | <b>54</b> |

| III          | Anexo  | 03.     |               | •••   | • • • |     | <br>    | • • • | <br>    | • • • |       |     | • • • | ••  |     |     |     | ••  | • • • |     |     |     |       |       | • • • | , <b></b> |       | 57        |

| IV           | Anexo  | 04.     |               | •••   | • • • |     | <br>    | • • • | <br>    | • • • |       |     | • • • | ••  |     |     |     | ••  | • • • |     |     |     |       |       | • • • | , <b></b> |       | 72        |

| $\mathbf{V}$ | Anexo  | 05.     |               |       |       |     | <br>    |       | <br>    |       |       |     |       |     |     |     |     |     | • • • |     |     |     |       |       |       |           |       | <b>74</b> |

# LISTA DE FIGURAS

| 1.1   | Crescimento no número de usuários mundial                                          | 1  |

|-------|------------------------------------------------------------------------------------|----|

| 2.1   | Exemplo de uso de sistemas embarcados                                              | 5  |

| 2.2   | Processador com arquitetura ARM                                                    | 6  |

| 2.3   | Arquitetura básica de um Arranjo de Portas Lógicas                                 | 7  |

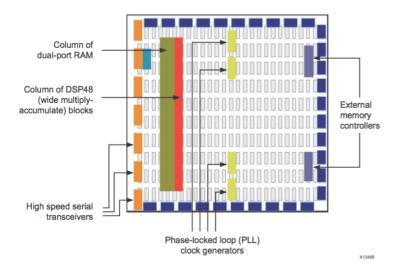

| 2.4   | Arquitetura de uma FPGA contemporânea                                              | 8  |

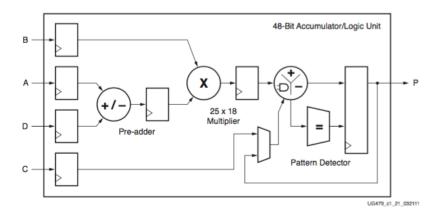

| 2.5   | Estrutura básica de um $DSP48$                                                     | 9  |

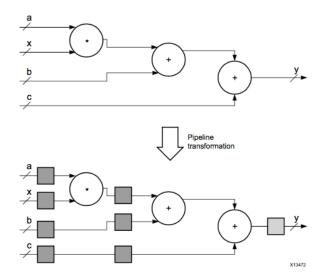

| 2.6   | Implementação de <i>pipeline</i> em um circuito                                    | 10 |

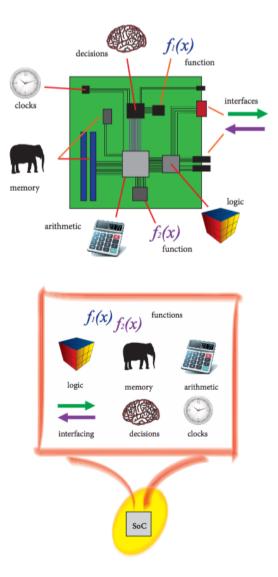

| 2.7   | Comparação de System-on-a-Board e System-on-Chip                                   | 11 |

| 2.8   | Kit de desenvolvimento Zedboard                                                    | 12 |

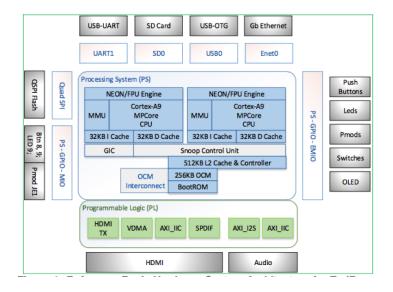

| 2.9   | Diagrama em blocos da Zedboard e seus periféricos                                  | 13 |

| 2.10  | Exemplo do uso do barramento AMBA                                                  | 14 |

| 2.11  | Estrutura AXI com as inter-conexões e interfaces entre PS-PL [4]                   | 15 |

| 2.12  | Arquitetura feedforward neural network                                             | 17 |

| 2.13  | Classificação em tempo de teste do LAST                                            | 19 |

| 3.1   | Texturas utilizadas para gerar o data base                                         | 24 |

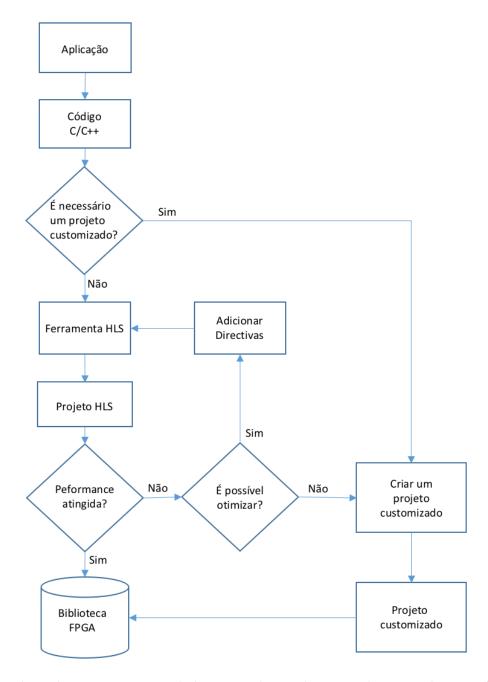

| 3.2   | Diagrama da solução Implementada                                                   |    |

| 3.3   | Diagrama da solução Implementada                                                   | 26 |

| 3.4   | Comparativo Tempo vs Performance da aplicação em um projeto [5]                    | 27 |

| 3.5   | Comparativo Tempo vs Performance da aplicação em um projeto [5]                    | 28 |

| 3.6   | Diagrama da solução Implementada Completa                                          | 29 |

| 4.1   | Quantidade de recursos utilizados nas soluções do problema reduzido não otimizado. | 33 |

| 4.2   | Quantidade de recursos utilizados nas soluções do problema reduzido otimizado      | 34 |

| 4.3   | Fluxo de projeto em FPGA.                                                          | 36 |

| I.1   | Quantidade estimada de recursos                                                    | 45 |

| I.2   | Projeto Vivado                                                                     | 46 |

| III.1 | Projeto Vivado                                                                     | 60 |

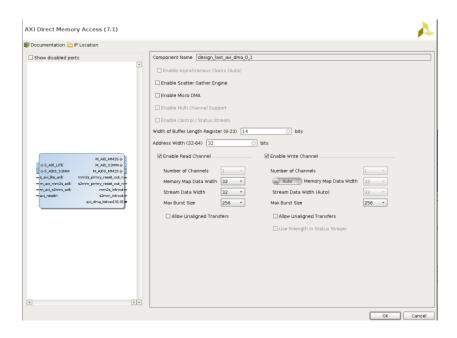

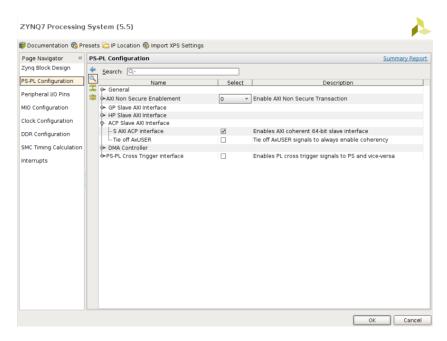

| III.2 | Configuração DMA                                                                   | 61 |

| III.3 | Configuração Zynq                                                                  | 61 |

# LISTA DE TABELAS

| 2.1 | Interface entre PS-PL                                                         | 15 |

|-----|-------------------------------------------------------------------------------|----|

| 4.1 | Resultados para o problema com dimensão 144 × 50 utilizando $AXI\text{-}Lite$ | 32 |

| 4.2 | Resultados para o problema reduzido utilizando $\mathit{AXI-Lite}$            | 33 |

| 4.3 | Resultados para o problema reduzido utilizando AXI-Stream                     | 34 |

## Capítulo 1

# Introdução

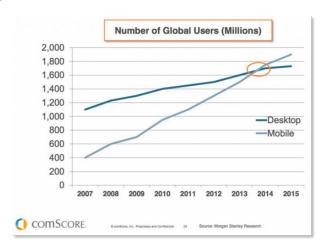

O uso de dispositivos eletrônicos móveis, como *smartphones* e *tablets* está mudando a forma como as pessoas interagem com o mundo, seja para trabalho, estudo ou entretenimento. A cada ano que se passa, constata-se um aumento no uso desses dispositivos. A Figura 1.1 ilustra o crescimento do número de usuários em plataformas móveis comparado com o número de usuários em plataformas *desktop* entre os anos de 2007 a 2015.

Figura 1.1: Crescimento no número de usuários mundial nas plataformas movéis e desktop. É interessante observar que no ano de 2015 o número de usuários em plataformas móveis é superior que o número de usuário desktop [6].

Um dos fatores que incentivaram essa migração é o uso de redes sociais para compatilhamento de imagens como Facebook, Google+, Instagram e outros, sendo que esses aplicativos fornecem ao usuário uma série de recursos para processamento de imagem, como filtros e reconhecimento facial de pessoas em fotos, marcando-as automaticamente. Com o desenvolvimento dos dispositivos móveis e embarcados, diversas aplicações usualmente executadas em computadores tem migrado para este tipo de plataforma, caracterizada principalmente pelas restrições em termos de capacidade de processamento, armazenamento e comunicação. Dentre as aplicações embarcadas, outro exemplo relevante de processamento de imagens são os sistemas de visão computacional embarcados em veículos autônomos, tais como os desenvolvidos pela Google e Tesla Motors, Mercedes-Benz e General

Motors. Foi com essa motivação, o crescente uso de dispositivos móveis, o uso de processamento de imagem em sistemas de visão computacional, como a identificação das pessoas em uma foto, robótica móvel, processamento em tempo real, eletrônica embarcada, que nasceu o interesse de desenvolver um sistema de classificação de imagens otimizado para sistemas embarcados.

O presente trabalho mostra a implementação de um classificador de imagens em um Sistema em Chip Programável (SoPC, do inglês System on Programmable Chip), que são largamente utilizados em dispositivos móveis devido a redução no tamanho do chip e no custo de fabricação em larga escala.

### 1.1 Contextualização

No âmbito dos algoritmos de reconhecimento de imagens e localização de objetos, constatase um crescente interesse na aplicação de redes neurais artificiais estilo feedforward (FNN, do inglês, feedforward neural network) [1] [7] [8]. Entretanto, essa topologia de rede ainda é difícil de ser implementada em sistemas embarcados, seja pelas restrições em termos de desempenho em tempo de teste ou armazenamento de dados [9]. A comunidade científica vem pesquisando técnicas visando reduzir a quantidade de recursos necessários à implementação de uma FNN, especialmente quando são utilizadas múltiplas camadas. Uma das técnicas estudadas na literatura para redução da quantidade de armazenamento necessário a descrição de uma FNN é a compressão de dados. Em [10] os autores pesquisaram métodos de comprimir os pesos da rede através da quantização dos vetores. Outras técnicas de compressão também têm se mostrado interessantes, como a weight pruning [11], onde os autores comprimiram para 40% a massa de dados do seu tamanho anterior.

A literatura sobre o tema é vasta e, consequentemente, só será apresentada algumas das tendências mais significativas. Além disso, é importante notar que as estratégias de quantização para reduzir o custo dos recursos de hardware em classificadores FNN implementadas em FPGA não são novas e foram utilizados no século passado com sucesso. Em [12] por exemplo, um modelo de quantização é proposto para eliminar todas as multiplicações durante o tempo de teste. Depois de treinar os parâmetros de uma rede neural, o autor discretiza esses parâmetros para uma potência de dois e retreina a rede, deixando apenas os valores de bias para mudar livremente no domínio real, uma vez que estes valores de bias não participam das multiplicações. Isso reduz cada multiplicação para uma única operação de deslocamento de bits. O problema com essa abordagem é que ela ainda depende de operações de ponto flutuante, que são caras em aplicações com quantidade de energia limitada e/ou pequeno poder computacional.

Em [13], [14] e [15], diferentes estratégias de quantização são apresentadas para permitir o uso de valores em ponto fixo durante o tempo de treinamento e teste. Entretanto, esses trabalhos não possuem o benefício da quantização para potências de dois, que elimina as multiplicações como em [12] [16] [3]. É possível que esse tipo de quantização fosse desconhecido pelos autores.

Em [17], os autores começam a experimentar com modelos de quantização que permitem uma grande redução de custo computacional. Eles usam a aproximação com potência de dois em fase de treinamento e na fase de classificação eles quantizam os parâmetros de rede para ter apenas -1s

e 1s. Isso reduz as multiplicações para simples mudanças de sinal seguido por adições apenas com uma pequena diminuição da precisão na classificação. Em [18] e [19] também é visto a mesma vantagem. Essa quantização é drástica e elimina todas as multiplicações e deslocamento de *bit* em tempo de teste, mas pode reduzir substancialmente a capacidade de aprendizagem da rede neural.

Em [20], os autores propõem um modelo de pós-processamento para aproximar os parâmetros treinados de uma rede neural convolucional (CNN, do inglês *Convolutional Neural Networks*) e os filtros para valores binários. Esta abordagem permite aproximar as convoluções para operações digitais do tipo XNOR e operações de contagem de *bits*. No entanto, esta simplificação vem com o preço de uma maior degradação na precisão da classificação em relação ao classificador original.

Para a implementação dos algoritmos baseados em rede neural, o uso de soluções heterogêneas vêm demonstrando o potencial benefício de redução de custos, especialmente em energia dissipada, como em [21], no qual os autores portaram o algoritmo de detecção automática de alvo e de classificação (ATDCA, do inglês Automatic Target Detection and Classification Algorithm) para a classificação de imagens hiperespectrais para uma unidade de processamento gráfico (GPUs, do inglês Graphics Processing Unit).

Outras aplicações incluem o uso de processadores digitais de sinais (DSPs, do inglês Digital Signal Processor), como em [22], no qual um sistema de classificação de imagens foi embarcado para a detecção automática de pequenos defeitos na confecção têxtil. Além disso, Arranjo de Portas Programáveis no Campo (FPGA, do inglês Field Programmable Gate Array) têm sido também utilizados para embarcar algoritmos do estado da arte da classificação de imagens, como em [23], no qual os autores embarcaram uma máquina de vetores de suporte (SVM, do inglês Support Vector Machine) para a detecção de pedestres, resultando em um desempenho que permitiu o sistema classificar 64 imagens de alta resolução (1920 x 1080 pixels) por segundo.

A abordagem xQuant [3] difere em muitos pontos desses métodos mencionados acima. Em primeiro lugar, ele pode ser facilmente adaptado a qualquer algoritmo de aprendizagem, uma vez que não depende de um específico, e, portanto, pode ser usado em diferentes arquiteturas de rede e diferentes quantidades de neurônios. Também, xQuant pode ser aplicada após o treinamento do classificador. Assim, a fase de aprendizagem podem ser executada usando muitos algoritmos maduros baseados em GPU, onde se tem a liberdade para explorar muitas arquiteturas e técnicas de aprendizagem diferentes. Em segundo lugar, ele substitui todas as operações em ponto flutuante/ponto fixo para valores em inteiros. Isso evita as técnicas de normalização e desnormalização, processos caros que são exigidos em operações de ponto flutuante. Em terceiro lugar, tem uma estratégia opcional para reduzir a faixa dinâmica dos parâmetros durante o treinamento e, consequentemente, reduzir o número de bits necessários para armazená-los. Esta estratégia penaliza parâmetros que provocam um aumento na faixa dinâmica, forçando-os a estar mais perto da média. Em quarto lugar, xQuant não diminui muito a acurácia da classificação como a binarização realizada em [20].

### 1.2 Perguntas de Pesquisa

Esta pesquisa visa avaliar a diferença na performance e na acurácia ao se utilizar técnicas de aceleração como o xQuant [3] em algoritmos de classificação com arquitetura baseada em redes neurais. O estudo da aceleração do classificador é dividido em três abordagens, sendo a primeira abordagem a utilização de técnicas convencionais em software, a segunda consiste em utilizar as técnicas convencionais, mas utilizando FPGAs para realizar o processamento da rede neural e a terceira abordagem que é utilizando técnicas xQuant.

- Solução 1: implementar o classificador por completo em *software* e executar em um processador de arquitetura ARM.

- Solução 2: implementar a extração de características e a aplicação do limiar do classificador em co-processador feito em FPGA.

- Solução 3: aplicar as técnicas xQuant [3] na Solução 2.

Logo tem-se como perguntas de pesquisa:

- 1. Qual a redução no tempo de processamento que se tem com o uso de um co-processador feito em FPGA para acelerar as operações mais custosas do classificador?

- 2. Em relação à Solução 3, qual a redução no tempo de processamento que se obtém? Qual a redução de área que se tem? Qual o impacto na acurácia de classificação?

### 1.3 Objetivo Geral

A proposta deste trabalho é analisar os impactos da implementação em FPGA de técnicas de otimização de um algoritmo de classificação de imagens que utiliza Redes Neurais estilo *Feed Forward*. As técnicas de otimização empregadas foram propostas em pesquisa de doutorado [3].

## 1.4 Objetivo Específico

Como objetivo específico decidiu-se por quantificar o impacto no tempo de processamento com o uso de um co-processador gerando um indicador a ser utilizado nas comparações entre as implementações feita em software, co-processador utilizando ponto flutuante e co-processador utilizando técnicas de otimizações xQuant. Além da avaliação do impacto em termos de desempenho foram avaliados também os impactos em termos de acurácia do algoritmo e a quantidade de recursos de hardware necessários à sua implementação.

## Capítulo 2

# Fundamentação Teórica

Nesse capítulo será apresentada uma revisão bibliográfica com a finalidade de familiarizar o leitor com os conceitos abordados neste trabalho, tais como: sistemas embarcados; arquitetura de processadores ARM; circuitos recofiguráveis; classificadores; o classificador LAST e as técnicas de otimização xQuant.

#### 2.1 Sistemas Embarcados

Os sistemas embarcados estão mudando a forma como as pessoas vivem, trabalham, estudam, se divertem e interagem. Exemplos de tais sistemas (Figura 2.1) são os MP3 players, o sistema de controle dos automóveis (computador de bordo, sistema ABS), os fornos de microondas com controle de temperatura inteligente, as máquinas de lavar e outros eletrodomésticos.

Figura 2.1: Exemplo de uso de sistemas embarcados - À esquerda tem-se o computador de bordo e o sistema ABS, à direita o sistema de controle das lentes em uma máquina fotográfica.

Conforme é definido em [24], "Sistemas embarcados são sistemas de processamento de informação incorporados em um produto maior".

Diferentemente de computadores de propósito geral, como o computador pessoal, um sistema embarcado realiza um conjunto de tarefas pré-definidas, geralmente com requisitos específicos. Já que o sistema é dedicado a tarefas específicas, através de engenharia pode-se otimizar o projeto, reduzindo tamanho, recursos computacionais e custo do produto.

Nos primeiros anos dos computadores digitais, na década de 1940, os sistemas embarcados

eram dedicados a uma única tarefa. Eram, entretanto, muito grandes para serem considerados embarcados. O primeiro sistema embarcado reconhecido mundialmente foi o *Apollo Guidance Computer*, desenvolvido nos EUA por Charles Stark Draper no MIT para a NASA. O "computador de guia", que operava em tempo real, era considerado o item eletrônico mais arriscado do projeto Apollo. No projeto desenvolvido pelo MIT foram usados circuitos integrados monolíticos, para reduzir o tamanho e peso do equipamento e aumentar a sua confiabilidade [25].

Sistemas embarcados utilizam vários tipos de processadores: DSPs, microcontroladores, microprocessadores. Ao contrário do mercado de computadores pessoais, que é basicamente dominado pelos processadores de arquitetura x86 da Intel/AMD, sistemas embarcados utilizam amplamente as arquiteturas ARM, PowerPC, PIC, AVR, 8051, Coldfire, TMS320, blackfin.

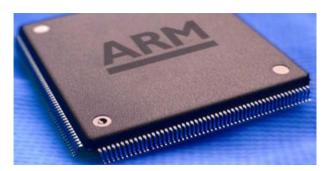

#### 2.1.1 Processadores ARM

Inicialmente desenvolvido pela Acorn Computers Limited de Cambridge, Inglaterra, entre outubro de 1983 e abril de 1985, a arquitetura ARM (primeiramente Acorn RISC Machine, atualmente Advanced RISC Machine), foi o primeiro processador RISC desenvolvido para uso comercial, projeto baseado no processador Berkeley RISC I [26]. Atualmente os processadores ARM (Figura 2.2) são 90% dos processadores embarcados RISC de 32 bits [27].

Figura 2.2: Processador com arquitetura ARM. Atualmente a maioria dos sistemas embarcados utilizam processadores com arquitetura ARM, devido ao baixo consumo de energia e o tamanho do núcleo reduzido.

#### Principais Características:

- Arquitetura Load-Store: as operações sobre dados são realizadas sobre os registradores. O

acesso à memória é realizado por instruções específicas que transferem dados entre memória

e registradores;

- Instruções fixas de 32 bits de largura (com exceção das instruções Thumb compactas de 16 bits) alinhadas em 4 bytes consecutivos da memória, com execução condicional, com poderosas instruções de carga e armazenamento de múltiplos registradores, capacidade de executar operações lógico-aritméticas em um único ciclo de relógio;

- 15 registradores de 32 bits para uso geral;

- Manipulação de periféricos de I/O como dispositivos mapeados na memória com suporte à interrupções;

- Conjunto de instruções aberto a extensões através de co-processador, incluindo a adição de novos registradores e tipos de dados ao modelo do programador;

- Baixo Consumo de energia;

- Tamanho do núcleo reduzido;

Por apresentar um baixo consumo de energia e menor custo, a arquitetura ARM tornou-se muito popular em aplicações de sistemas embarcados.

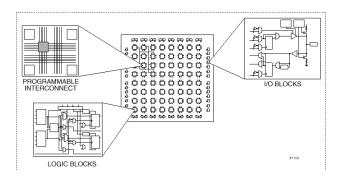

#### 2.1.2 Field Programmable Gate Array - FPGA

Arranjo de Portas Programável em Campo (FPGA, do inglês *Field Programmable Gate Array*) é um circuito integrado que após a fabricação pode ser programado para executar lógica digital.

Figura 2.3: Arquitetura básica de um Arranjo de Portas Lógicas, composta basicamente por blocos lógicos, blocos com interface de entrada/saídas e a interconexão programável.

A estrutura básica de um FPGA (Figura 2.3) consiste nos seguintes elementos:

- Look-up table (LUT): Elemento responsável por armazenar as operações lógicas;

- Flip-Flop (FF): Elementos responsáveis por salvar os resultados das LUT;

- Wires: Elemento que conecta elementos;

- Input/Output (I/O) pads: Portas físicas utilizadas para entrada/saída de dados da FPGA.

A combinação desses elementos resulta na arquitetura básica de um FPGA, entretanto, as arquiteturas de FPGA mais contemporâneas contêm blocos de armazenamento de dados aumentando a densidade e eficiência computacional do dispositivo. Os elementos adicionados são:

- Memória embarcada para o armazenamento de dados;

- Phase-locked loops (PLLs) para a geração de diferentes frequências de clock;

- Controladores de memória;

- Blocos de multiplicação/Acumulador;

Com a combinação desses elementos citados, tem-se a arquitetura de um FPGA contemporânea, conforme é visto na Figura 2.4

Figura 2.4: Arquitetura de uma FPGA contemporânea [5]. Diferente da arquitetura básica, a arquitetura contemporânea traz novos blocos com a intenção de reduzir o custo de recursos (LUTs e FFs) que eram anteriormente utilizados para gerar esses novos blocos. Agora o projetista pode utilizar diretamente esses novos elementos, como blocos de multiplicação / acumulador, blocos de memória.

#### 2.1.2.1 Arquitetura FPGA

A seguir são listados os conceitos dos principais recursos utilizados na FPGA, como LUT, FF, DSP, BRAM. Esses foram os mesmos elementos utilizados na comparação de redução de custo computacional na implementação do classificador de imagens.

#### • Look-up Table - LUT

A LUT é o bloco básico da FPGA, sendo capazes de implementar qualquer função lógica de N variáveis booleanas. A LUT é essencialmente uma tabela verdade, o limite do tamanho dessa tabela é  $2^N$ , sendo N o número de entradas. A implementação em hardware de uma LUT pode ser feita através de uma coleção de células de memórias conectadas à multiplexadores.

#### • Flip-Flop

O *flip-flop* é o elemento básico para armazenamento em uma FPGA. Esse elemento é sempre combinado com uma LUT para suportar o projeto de circuitos sequenciais e armazenamento de dados.

#### • DSP

O DSP é o elemento mais complexo bloco computacional disponível em um FPGA. O DSP é uma unidade lógica aritmética (ALU, do inglês arithmetic logic unit), o qual é composto por uma cadeia de três diferentes blocos, que são:

- Unidade soma/subtração;

- Unidade multiplicação;

- Unidade soma/subtração/acumulador.

A Figura 2.5 mostra a estrutura básica do DSP48. O DSP48 pode ser usado como multiplicador  $25 \times 18$ , ou seja multiplica palavras de  $25\ bits$  por palavras de  $18\ bits$ , também é utilizado como acumulador de  $48\ bits$  ou como detector de padrões.

Figura 2.5: Estrutura básica de um DSP48 [28]. O DSP é um elemento comumente visto nas arquiteturas contemporâneas de FPGA, com o intuito de disponibilizar ao projetista um bloco otimizado para realizar operações matemáticas. O DSP é um elemento usualmente utilizado para realizar medições, filtros e compressão de sinais.

#### • BRAM

A BRAM (block random-access memory) é um módulo RAM dual-port externo acessado pela FPGA para armazenar dados relativamente grandes.

#### 2.1.2.2 Paralelismo no FPGA

Um dos recursos disponibilizados com o uso de FPGA é executar operações em paralelo, recursos comumente utilizados para acelerar a execução da lógica. As técnicas mais comumente utilizadas são o escalonamento, o *pipeline*.

#### • Escalonamento

O escalonamento define quando as operações devem ser realizadas, tendo como referência de tempos ciclos de relógio. O processador deve respeitar restrições de projeto, tais como número máximo de ciclos para realização da tarefa e número de operações paralelas por ciclo.

#### Pipelining

O pipelining é uma técnica utilizada em projeto digital baseada na divisão de uma tarefa em subtarefas sequenciais processadas de forma sinultânea. As subtarefas correspondem aos estágios do pipeline que são delimitados por registradores. A Figura 2.6 mostra o processo de transformação, em vez de esperar o ciclo completo (multiplicação-soma1-soma2), conforme é visto, com a inserção dos estágios é possível já começar o próximo ciclo sem o primeiro ter terminado.

Figura 2.6: Implementação de *pipeline* em um circuito [28]. Esse exemplo mostra a implementação de um *pipeline* em um circuito somador de 4 entradas e 1 saída, sendo que cada estágio é criado com a inserção do elemento FF.

#### Dataflow

O princípio básico das arquiteturas dataflow é que a execução das operações é acionada em função da disponibilidade dos operandos. Ela não segue uma estrutura convencional da máquinas algorítmicas, onde uma parte de controle é responsável pela sincronização das operações.

#### 2.1.3 System on Chip - SoC

Sistema em *Chip* (SoC, do inglês *System-on-Chip*) consiste na união de subsistemas em uma única pastilha de silício, integrando componentes digitais, analógicos e de rádio frequência. A

solução em SoC provê uma transferencia mais rápida e mais segura de dados, menor consumo de energia e uma redução física de área.

A Figura 2.7 compara um sistema digital com blocos de processamento, lógica de alta velocidade, interface e memória feito em uma placa de circuito impresso (PCB, do inglês *Printed Circuit Board*) com um sistema SoC.

Figura 2.7: Comparação de *System-on-a-Board* e *System-on-Chip* [4]. Um *System-on-Chip* reúne as principais funcionalidades, como blocos de memória, lógica digital, tomada de decisão, que antigamente era desenvolvido por um circuito em uma única pastilha de silício.

Para a realização do projeto que consta nesta dissertação foi utilizada a arquitetura Zynq desenvolvida pela Xilinx, essa arquitetura recebe a denominação de All-Programmable SoC - APSoC, diferente de um sistema SoC padrão. A arquitetura APSoC introduz a idéia de um sistema reconfigurávél em um SoC, trazendo uma maior flexibilidade em projetos que utilizam microprocessadores e FPGA.

Figura 2.8: Kit de desenvolvimento Zedboard

O kit de desenvolvimento utilizado foi *Digilent Zedboard*, Figura 2.8,baseada em um Xilinx Zynq-7020 arquitetura SoC. Esse SoC integra um sistema ARM Cortex-A9 *dual core* de processamento (PS) e uma 28nm Xilinx Series-7 lógico programável (PL). Ele tem uma forte integração do microprocessador incorporado e do FPGA realizada pelo barramento (AMBA) de interfaces AXI4. Como características do kit de desenvolvimento *Digilent Zedboard* tem-se:

- Zynq-7000 AP SoC XC7Z020-CLG484;

- Dual-core ARM Cortex A9 1GHz;

- Memória:

512 MB DDR3;

256 Mb Quad-SPI Flash;

4 GB SD card

O kit Xilinx Zedboard possui dois módulos para desenvolvimento, o primeiro módulo é denominado Sistema de Processamento (PS, do inglês Processing System), através desse sistema é possível executar um sistema operacional embarcado, também é possível utilizá-lo em Bare Metal, ou seja sem o uso de um sistema operacional. O segundo módulo utilizado para desenvolvimento é denominado Lógica Programavel (PL, do inglês Programmable Logic), com esse módulo o desenvolvedor tem acesso a Zynq-7000 AP SoC, utilizado para circuitos reconfiguráveis, ou seja no projeto de hardware dedicado.

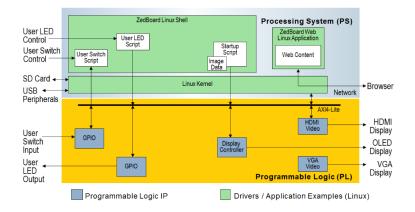

O uso do módulo PL é recomendado para implementação de lógica de alta velocidade, aritmética, fluxo de dados, enquanto o módulo PS suporta rotinas em *software* e/ou sistema operacional. A Figura 2.9 mostra a arquitetura básica, para os dois módulos citados PS e PL, com seus periféricos.

O Zynq-7000 PL é um Artix-7 contendo  $106\,400~flip$ -flops (FF),  $53\,200~look$ -up tables (LUT), 140~blocos de 36Kb usados como RAM (LUTRAM), e 220~DSP ( $18\times25$ ). O PL e PS estão

Figura 2.9: Diagrama em blocos da Zedboard e seus periféricos

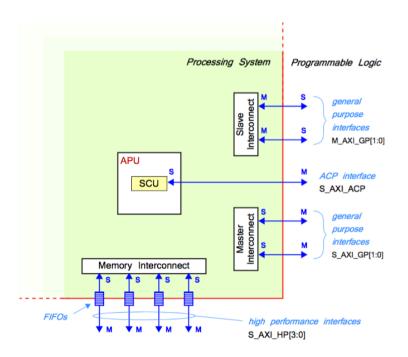

conectados através das seguintes interfaces AXI4: quatro interfaces de uso geral AXI de 32 bits, 2 mestres e 2 escravos; interfaces de 64-bits AXI de alto desempenho; e um AXI ACP 64-bit (*Accelerator Coherency Port*) interface escravo, que é conectado diretamente à unidade de controle *snoop* (SCU, do inglês *snoop control unit*) de memória *cache* L2 e fornece ponto de acesso assíncrona a *cache* diretamente do PL para a CPU Cortex-A9 subsistema de processador [29].

#### 2.1.4 Comunicação entre ARM & FPGA

A comunicação entre o processador ARM e a FPGA se dá por meio de interconexões presente no SoC, chamadas de barramento. Um barramento é um conjunto de linhas de comunicação utilizada para envio/recebimento de dados e controle de periféricos.

A escolha do barramento se torna crucial, já que é esse que pode limitar a velocidade da comunicação entre os módulos PS e PL. A seguir são listados os principais barramentos utilizados em um SoC.

- Core-Conect;

- WishBone;

- AXI;

Em [30] é possível ver um estudo detalhado a respeito dos barramentos mais utilizados em SoC. O kit Zedboard utiliza como interconexão entre o módulo PL e PS a interface AXI - Advanced eXtensible Interface, a interface AMBA mais difundida. A Figura 2.10 mostra um exemplo do uso do barramento AMBA utilizando a interface AXI para troca de dados entre o Sistema de Processamento(PS) e a Lógica Programável(PL).

Figura 2.10: Exemplo do uso do barramento AMBA

A escolha do protocolo para o barramento AXI depende das propriedades desejadas nas conexões.

- AXI4 Para ligações de memória mapeada, um endereço é fornecido seguido por uma transferência contínua de dados de até 256 palavras de dados ( $data\ beats$ );

- AXI4-Lite Uma ligação simplifica, onde apenas um dado é transferido por conexão;

- AXI4-Stream para streaming de dados suportando transferência contínua de dados, não existindo nenhum mecanismo de endereço. Esse tipo de protocolo é indicado para fluxo de dados entre fonte e destino (sem memória mapeada).

A conexão com o barramento dos módludos PS-PL se dá através de interfaces, sendo que cada interface possui o seu uso recomendado, seja para controle de periféricos, envio de dados.

- General Purpose AXI Barramento de dados de 32-bits, com baixa e média taxa de comunicação entre PL e PS. A interface é direta e não inclui buffering;

- Accelerator Coherency Port Barramento de dados de 64-bits, uma conexão assíncrona entre PL e SCU dentro da APU. Essa interface é usada para forçar a coerência entre as caches APU e os elementos dentro de PL;

- High Performance Ports Esse barramento pode ser de 32-bits ou 64-bits. Para realizar o comportamento de rajada (burst), é incluido um buffer utilizando FIFO.

A Tabela 2.1 mostra um resumo mostrando quem é o mestre/escravo nas transações efetuadas para cada interface citada anteriormente.

| Interface | Descrição                                                           | Mestre | Escravo |

|-----------|---------------------------------------------------------------------|--------|---------|

| M_AXI_GP0 | GENERAL PURPOSE (AXI_GP)                                            | PS     | PL      |

| M_AXI_GP1 | GENERAL I ORI OSE (AXI_GI)                                          | PS     | PL      |

| S_AXI_GP0 | GENERAL PURPOSE (AXI_GP)                                            | PL     | PS      |

| S_AXI_GP1 | GENERAL FURFOSE (AXI_GF)                                            | PL     | PS      |

| S_AXI_ACP | Accelerator Coherency Port (ACP) Transação de coerência entre cache | PL     | PS      |

| S AXI HP0 | Transação de coerciicia entire caene                                | PL     | PS      |

| S AXI HP1 | High Performance Ports (AXI_HP)                                     | PL     | PS      |

| S_AXI_HP2 | Com leitura/escrita FIFO                                            | PL     | PS      |

| S_AXI_HP3 |                                                                     | PL     | PS      |

Na Figura 2.11 fica mais evidente como cada interface está conectada com o módulo PS evidenciando o motivo de cada interface ter o seu propósito de uso, como a interface ACP está conectada diretamente com o SCU do processador, mais indicado para transfarência de dados, a interface GP pode ser utilizada como mestre, sendo mais indicado o seu uso para controle de periféricos, por exemplo LEDs. A interface HP tem uma conexão com a memória, interface que também é recomendada para transferência de dados.

Figura 2.11: Estrutura AXI com as inter-conexões e interfaces entre PS-PL [4].

## 2.2 Classificador de Imagem com Arquitetura em Rede Neural

Nessa seção será apresentado o conceito de um classificador de imagens com arquitetura em rede definindo o que é um classificador, conceituando o que é uma arquitetura em rede e a formulação do classificador de imagem utilizado nesse trabalho para a implementação em *hardware*.

#### 2.2.1 Conceito de Classificador

Imagens são adquiridas com a ajuda de dispositivos ópticos que podem conter milhões de transdutores fotossensíveis dispostos em matrizes geralmente rectangulares. Os sinais elétricos resultantes variam continuamente de acordo com a quantidade de luz que atinge o sensor em um tempo específico. Uma imagem estática é então formada por digitalização destes sinais elétricos com a ajuda de um ADC. A saída pode ser vista como uma matriz contendo os valores inteiros que representam a amplitude do sinal em cada um dos transdutores em um momento específico. Cada um destes valores, com o nome de *pixels*, pode variar entre 0 a  $2^n - 1$ , onde n é a quantidades de *bits* do ADC. As cores da imagem podem ser separadas utilizando filtros ópticos situados na parte superior de cada matriz de transdutores fotossensíveis.

Depois que as imagens são digitalizadas, elas podem ser classificadas como qualquer outro sinal digital. Formalmente, uma classificação de sinal pode ser definida como segue. Seja  $(\mathbf{X}, \mathbf{y})$  um conjunto de sinais, onde  $\mathbf{X}$  contém n sinais  $\mathbf{x} = [x_1, x_2, \dots, x_m] \in \mathbb{R}^m$ , associada à uma das possíveis classes k e  $y \in \{1, 2, \dots, k\}$ . Sendo  $y_i = f(\mathbf{x}_i)$ ,  $i = 1, \dots, n$  seja f a função desconhecida que define a relação entre os sinais e suas respectivas classes. O problema de classificação consiste em encontrar uma função  $\hat{f}(\mathbf{x})$  que melhor se aproxima de  $y_i = f(\mathbf{x}_i)$ , com  $i = 1, \dots, n$  de forma que o erro médio quadrado (MSE, do inglês Mean Squared Error)

$$\arg\min_{\hat{f}(\mathbf{x})} \sum (y_i - \hat{f}(\mathbf{x}_i))^2 \ \forall i = 1, \dots, n,$$

(2.1)

seja minimizado, não só para os sinais a partir do conjunto de treinamento  $\mathbf{X}$ , mas também para os sinais desconhecidos, aqueles que não foram apresentadas ao algoritmo de aprendizagem. Há um trade-off implícito entre minimizar o erro para o conjunto de treinamento e os sinais desconhecidos [9]. Por isso, é importante que a aprendizagem do classificador não se torne sobreajustado (overfitted) para os sinais de conjunto de treinamento de modo que se pode generalizar para sinais desconhecidos. A função  $\hat{f}(\mathbf{x})$  que melhor aproxima  $f(\mathbf{x})$  e não é sobre-ajustado para  $\mathbf{X}$  pode ser encontrado usando métodos matemáticos de otimização, tais como otimização numérica [31] [32].

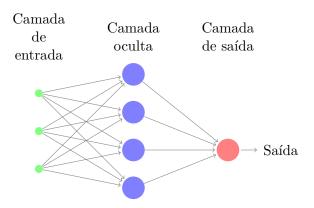

Uma FNN é uma arquitetura biologicamente inspirada em redes neurais, que consiste de um conjunto de unidades de processamento organizado em camadas, onde cada unidade se assemelha a um neurônio biológico, ou seja, uma função de transferência que tem muitas entradas e uma saída. Como mostrado na Figura. 2.12, a arquitectura de uma FNN é um gráfico acíclico dirigido em que cada neurônio na camada anterior está ligada à camada seguinte por um conjunto de pesos independentes, normalmente chamados parâmetros.

Esses neurônios podem ser ajustado adequadamente para aproximar funções complexas que podem depender de um grande número de entradas. Isso significa que a rede pode aprender a associar devidamente um conjunto de vetores de entrada em um conjunto de vetores de saída com um certo grau de precisão. Quando o conjunto de vetores de saída é depois usado para calcular a classe do vetor de entrada, a FNN é denominada como um classificador. Um exemplo de classificadores que são comuns hoje em dia é em reconhecimento de imagem, onde um classificador

Figura 2.12: Arquitetura de uma feedforward neural network contendo um único neurônio como saída.

FNN treinado pode, por exemplo, identificar pessoas em fotos.

Durante a fase de treinamento de um classificador, os seus parâmetros da rede são ajustados para associar um determinado conjunto de imagens de entrada para o conjunto da classe de entrada. Durante a fase de classificação, o classificador treinado é usado para classificar novos vetores de entrada e a maioria dos seus cálculos são multiplicações de matrizes-vetores, onde as imagens de entrada dispostas como vetores são multiplicadas pela matriz contendo os parâmetros aprendidos. Portanto, a classificação de imagens pode ser considerada como uma multiplicação de matrizes-vetores de valores em ponto flutuante, que pode ser eficientemente realizada em arquiteturas paralelas, tais como GPUs e FPGAs.

Um problema histórico de classificador com arquitetura FNN foi a dificuldade inerente em se treinar redes com mais de três camadas ocultas e, assim, eles eram geralmente limitados a problemas de baixa complexidade [33] [34]. A partir do ano de 2006, os avanços no processo de aprendizagem de classificadores FNN tornaram possível superar essas dificuldades e, consequentemente, as redes neurais profundas (DNN, do inglês *Deep Neural Networks*) começaram a superar diversos algoritmos do estado-da-arte em diversas tarefas difíceis, como reconhecimento de voz [2] e classificação de imagens [1], só para citar alguns. Esta descoberta veio com uma desvantagem: o grande número de multiplicações em ponto flutuantes necessárias em tempo de teste, a quantidade de memória necessária para armazenar os parâmetros treinados e a operação demorada de transferi-los da memória para a unidade de processamento. Esse é um problema desafiador até mesmo para implementações em FPGA [35].

Em [16] [3], foi mostrado que os parâmetros de um classificador FNN podêm ser reescalonados para valores inteiros e depois quantizados e aproximados cada um deles para potência de dois mais próxima. Quando estes parâmetros são utilizados para classificar imagens em inteiros, isto é, imagens representadas na forma que elas são emitidas pelos ADC, cada multiplicação em ponto flutuante é substituída por uma única operação de deslocamento de bits. Esse não é apenas mais rápido para executar em FPGA, mas também usa menos recursos e sem utilizar módulos DSP. Esse conjunto de técnicas foi nomeado xQuant [3]. Embora haja uma análise detalhada da técnica xQuant no trabalho, não havia nenhuma implementação feita em FPGA e, assim, não havia nenhuma análise do uso de recursos do FPGA.

Portanto, a motivação desse trabalho foi o de descobrir o quanto de recursos do FPGA é reduzido e quão mais rápido é a classificação em tempo de teste quando os parâmetros de um classificador FNN é quantizado utilizando a técnica xQuant. Dando continuidade ao trabalho [3], decidiu-se como estudo de caso o uso do algoritmo classificador FNN LAST (Learning Algorithm for Soft-Thresholding), para treinar o classificador, um conjunto de dados de imagens contendo retalhos de 36 pixels extraídos de duas imagens de textura, seguindo os mesmos passos usados em [36] [16] [3].

#### 2.2.2 Learning Algorithm for Soft-Thresholding (LAST)

O algoritmo de classificação Learning Algorithm for Soft-Thresholding - LAST [36] usado nas simulações é um algoritmo desenvolvido para aprender os parâmetros de um classificador FNN cuja arquitetura consiste em uma única camada oculta e uma camada de saída contendo apenas um neurônio, como mostrado na Figura 2.12. Diferentemente de redes neurais tradicionais, LAST tem como objetivo aprender uma transformada esparsa não linear na sua camada escondida e um vetor hiperplano de classificação na sua camada de saída. A parte não linear da transformada na camada escondida é realizada pela função de ativação

$$h_{\alpha}(\mathbf{z}) = \max(0, z - \alpha),\tag{2.2}$$

onde  $\alpha$  é fixado durante o treinamento, geralmente definido como 1. Essa função de ativação é semelhante à função de retificação  $g(x) = \max(0, x)$  que tem mostrado bons resultados em métodos de apendizagem profunda [37] [38] [39] [40].

LAST é treinado da seguinte forma: Seja  $(\mathbf{X}, \mathbf{y})$  o conjunto de treinamento, onde  $\mathbf{X} = [\mathbf{x}_i]_{i=1}^n$  é o conjunto de vetores sinais  $\mathbf{x}_i \in \mathbf{R}^m$ ,  $\mathbf{y} = [y_i]_{i=1}^n$  é o conjunto de classes, e cada vetor sinal de  $\mathbf{x}_i$  está associada a uma classe  $y_i \in \{-1, 1\}$ . A matriz  $\mathbf{D} \in \mathbb{R}^{m \times d}$ , que contém d neurônios, e o classificador hiperplano  $\mathbf{w} \in \mathbb{R}^d$  é estimado usando otimização supervisionada

$$\arg\min_{\mathbf{D}, \mathbf{w}} \sum_{i=1}^{m} L(\mathbf{y}_{i} \mathbf{w}^{\top} h_{\alpha}(\mathbf{D}^{\top} \mathbf{x}_{i})) + \frac{v}{2} \|\mathbf{w}\|_{2}^{2}, \tag{2.3}$$

onde L é a função de perda  $L(x) = \max(0, 1 - x)$  e v é o parâmetro de regularização que evita que o classificador  $\mathbf{w}$  fique sobreajustado ao conjunto de treinamento.

Em tempo de teste, o sinal de entrada  ${\bf x}$  deve ser normalizado para ter norma  $\ell_2$  igual 1 antes de ser classificado pela rede

$$classe = \begin{cases} +1 & \text{se } \mathbf{w}^{\top} \max(0, \mathbf{D}^{\top} \mathbf{x} - \alpha) > 0, \\ -1 & \text{caso contrário}, \end{cases}$$

(2.4)

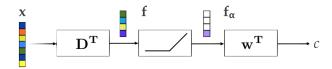

onde classe é a classe retornada pelo classificador. A Figura 2.13 mostra como LAST opera em tempo de teste.

Figura 2.13: Classificação em tempo de teste realizado pelo LAST. O sinal de entrada  $\mathbf{x}$  é primeiramente transformado de forma linear pela matriz  $\mathbf{D}$ , resultando no vetor  $\mathbf{f} = \mathbf{D}^{\top}\mathbf{x}$ . Em seguida, os valores de  $\mathbf{f}$  são retificados com o operador soft-threshold [41], tornando  $\mathbf{f}$  esparso com  $\mathbf{f}_{\alpha} = \max(0, \mathbf{f} - \alpha)$ . Por último, o vetor esparso  $\mathbf{f}_{\alpha}$  é classificado pelo vetor hiperplano  $\mathbf{w}$ , e assim a saída da rede é igual  $c = \mathbf{w}^{\top}\mathbf{f}_{\alpha}$ . A classe predita será 1 se c > 0 e -1 caso contrário. Esta figura foi adaptada de [36].

Vale ressaltar que os sinais de treinamento devem ser normalizados para ter norma  $\ell_2$  igual a 1 antes do treinamento. Isso é necessário, a fim de evitar instabilidade numérica nos cálculos realizados durante a fase de aprendizagem. Além disso, como ambos  $\mathbf{D}$  e  $\mathbf{w}$  são treinados com sinais normalizados, os sinais em tempo de teste também deve ser normalizados. É recomendada a leitura de [36] para mais informações.

O Algoritmo 1 mostra os procedimentos para implementar o classificador LAST em tempo de execução.

#### Algorithm 1 Algoritmo LAST

```

1: procedure LAST

// Carrega D, w, e X

D \leftarrow Carrega\ dicionario\ D

3:

X \leftarrow Carrega\ imagem

4:

w \leftarrow Carrega\ vetor\ classificador

5:

6:

7:

//Extração de características

aux \leftarrow D[i][k] * X[k][j]

8:

9:

//Aplica limiar: max(0,d*x - alpha))

10:

f_{\alpha} \leftarrow aux - alpha

11:

if f_{\alpha} < 0 then

12:

f_{\alpha} \leftarrow 0

13:

14:

//Aplica a classificação

15:

16:

c \leftarrow w * f_{\alpha}

if c >= 0 then

17:

labels \leftarrow 1

18:

19:

else

labels \leftarrow -1

20:

21:

```

### 2.3 Multiplicação Matriz-Matriz

Como visto na Seção 2.2.2, a multiplicação Matriz-Matriz é utilizada em tempo de teste na classificação, logo nessa seção são encontrados os principais meios de se realizar a multiplicação Matriz-Matriz.

#### 2.3.1 Algoritmo Padrão

Suponha a situação, na qual é necessário multiplicar uma matriz A com m linhas e n colunas por uma matriz B com n linhas e p colunas, resultando em uma matriz C.

$$A = \begin{bmatrix} a_{1,1} & \cdots & a_{1,n} \\ a_{2,1} & \cdots & a_{2,n} \\ \vdots & \ddots & \vdots \\ a_{m,1} & \cdots & a_{m,n} \end{bmatrix}, \quad B = \begin{bmatrix} b_{1,1} & \cdots & b_{1,p} \\ b_{2,1} & \cdots & b_{2,p} \\ \vdots & \ddots & \vdots \\ b_{n,1} & \cdots & b_{n,p} \end{bmatrix} \quad \text{e} \quad C = \begin{bmatrix} c_{1,1} & \cdots & c_{1,p} \\ c_{2,1} & \cdots & c_{2,p} \\ \vdots & \ddots & \vdots \\ c_{m,1} & \cdots & c_{m,p} \end{bmatrix}$$

$$C = A * B \tag{2.5}$$

O algoritmo padrão para multiplicação matriz-matriz consiste em multiplicar cada elemento da linha de uma matriz A por cada elemento da coluna de uma matriz B, onde cada multiplicação é somada e resulta em um elemento de saída da matriz C, conforme é mostrado na Equação (2.6)

$$c_{i,j} = \sum_{k=1}^{n} (a_{i,k} * b_{k,j})$$

(2.6)

#### 2.3.2 Multiplicação em Bloco

Para implementações que desejam realizar processamento em paralelo, um algoritmo recomendado é a multiplicação em bloco. O método consiste em particionar a matriz em matrizes menores, chamados de blocos.

Suponha que a matriz  $A_{m,n}$  é uma matriz com 6 linhas (m) e 6 colunas (n). O bloco maior é particionado até um limite de elementos definido por  $BB(basic\ block\ size)$ . O particionamento da matriz A com BB=3 é

$$A_{11} = \begin{bmatrix} a_{1,1} & a_{1,2} & a_{1,3} \\ a_{2,1} & a_{2,2} & a_{2,3} \\ a_{3,1} & a_{3,2} & a_{3,3} \end{bmatrix} A_{12} = \begin{bmatrix} a_{1,4} & a_{1,5} & a_{1,6} \\ a_{2,4} & a_{2,5} & a_{2,6} \\ a_{3,4} & a_{3,5} & a_{3,6} \end{bmatrix}$$

$$A_{21} = \begin{bmatrix} a_{4,1} & a_{4,2} & a_{4,3} \\ a_{5,1} & a_{5,2} & a_{5,3} \\ a_{6,1} & a_{6,2} & a_{6,3} \end{bmatrix} A_{22} = \begin{bmatrix} a_{4,4} & a_{4,5} & a_{4,6} \\ a_{5,4} & a_{5,5} & a_{5,6} \\ a_{6,4} & a_{6,5} & a_{6,6} \end{bmatrix}$$

$$A = \begin{bmatrix} A_{11} & A_{12} \\ A_{21} & A_{22} \end{bmatrix} \tag{2.7}$$

Após separar em blocos menores é possível realizar a multiplicação em paralelo de cada um desses sub-blocos utilizando o algoritmo padrão Equação (2.8).

$$c_{i,j} = \sum_{k=1}^{n} (a_{i,k} * b_{k,j})$$

(2.8)

#### 2.3.3 Algoritmo Strassen

O algoritmo de Strassen [42] é utilizado para reduzir o número de multiplicações, criando variáveis intermediárias (Equação (2.9)) e o resultado final (Equação (2.10)) é produzido com a combinação de somas e subtrações dessas variáveis intermediárias. O método pode apenas ser aplicado em matrizes da ordem de potência de 2  $(2^1, 2^2, 2^3, ..., 2^n)$ .

$$C = A * B$$

$$\begin{bmatrix} c_{11} & c_{12} \\ c_{21} & c_{22} \end{bmatrix} = \begin{bmatrix} a_{11} & a_{12} \\ a_{21} & a_{22} \end{bmatrix} * \begin{bmatrix} b_{11} & b_{12} \\ b_{21} & b_{22} \end{bmatrix}$$

$$s_{1} = (a_{1,1} + a_{2,2}) * (b_{1,1} + b_{2,2})$$

$$s_{2} = (a_{2,1} + a_{2,2}) * b_{1,1}$$

$$s_{3} = a_{1,1} * (b_{1,2} - b_{2,2})$$

$$s_{4} = a_{2,2} * (b_{2,1} - b_{1,2})$$

$$s_{5} = (a_{1,1} + a_{1,2}) * b_{2,2}$$

$$s_{6} = (a_{2,1} - a_{1,1}) * (b_{1,1} + b_{1,2})$$

$$s_{7} = (a_{1,2} - a_{2,2}) * (b_{2,1} + b_{2,2})$$

(2.9)

$$c_{1,1} = s_1 + s_4 - s_5 + s_7$$

$$c_{1,2} = s_3 + s_5$$

$$c_{2,1} = s_2 + s_4$$

$$c_{2,2} = s_1 - s_2 + s_3 + s_6$$

(2.10)

### 2.4 Aproximação para Potências de 2 mais Próximas (xQuant)

Como mencionado na Seção 1.1, as desvantagens de classificadores FNN são o grande número de multiplicações em ponto flutuante em tempo de teste, a grande quantidade de memória necessária para armazenar todos os parâmetros da rede, e o tempo de transferência desses parâmetros da memória para a unidade de processamento. Uma abordagem para esses problemas é o de quantizar adequadamente os parâmetros de rede após o treinamento. Nos trabalhos [16] [3], foi mostrado que os parâmetros de um classificador FNN pode ser redimensionada para valores inteiros e depois quantizados para potência de dois mais próximo, essa quantização extrema foi denominada de xQuant.

xQuant é um conjunto de técnicas de otimizações desenvolvida em [3], que são utilizadas em classificadores com arquitetura em rede não linear assim como o classificador LAST, o xQuant propõem uma mudança visando uma redução no número de recursos necessários na implementação do classificador em hardware, para isso, em [3] é mostrado de forma empírica que o dicionário e o vetor de classificação do algoritmo LAST, podem ser representados como potência de 2 e também que se pode classificar sinais inteiros sem degradação na precisão em comparação com a classificação de sinais normalizados.

Essas otimizações são atingidas ao se aplicar o conjunto de cinco técnicas, primeiramente devese aproximar o dicionário e as entradas do classificador para a potência de dois mais próxima, com a perda da precisão da classificação limitada. Essa técnica permite a substituição da operação de multiplicação por apenas um deslocamento de bits, que é uma das operações mais simples em hardware. A segunda técnica aplicada é a utilização de sinais em inteiro, em vez de ponto flutuante. Logo é possível a utilização de operações em inteiros que são de baixo custo computacional quando comparado com as operações em ponto flutuante, eliminando o uso de DSP. O terceiro procedimento é reduzir a faixa dinâmica do conjunto de teste de X. Com esse procedimento se reduz o número de bits necessários para a representação esparsa do sinal em teste. O próximo passo é reduzir a faixa dinâmica de entradas de dicionário durante o treinamento. Ao aplicar esse passo, reduz-se o número de bits necessários para a representação do dicionário, reduzindo, assim o custo necessário para armazenagem do dicionário e um ganho de performance já que uma quantidade menor de bits para processar as operações é necessária.

Seja **D** o conjunto que contém todos os parâmetros de uma camada de um classificador FNN e  $p_{min} = \min(|\mathbf{D}|)$  tal que  $p_{min} \neq 0$ . **D** é redimensionado dividindo seus elementos por  $p_{min}$  seguido por uma operação de arredondamento, ou seja, o novo conjunto reescalonado  $\mathbf{D}_{xquant} =$

round( $\mathbf{D}/p_{min}$ ). Em seguida,  $\mathbf{D}_{xquant}$  é iterativamente quantizada dividindo seus elementos por dois e arredondando-os. Por fim, cada  $p \in \mathbf{D}_{xquant}$  é aproximado para potência de dois mais próximo. Seja  $p_{max} = \max(|D_{xquant}|)$  e  $q_{bits} = \lfloor \log_2(\max|\mathbf{D}_{xquant}|) \rfloor + 1$ . Cada w será então representado por valores entre  $-(2^q)$  a  $2^q$ , com q variando de 0 a  $q_{bits}$ . A multiplicação desses valores corresponde ao deslocamento de q bits. Para armazenar o sinal, apenas um bit é necessário, e para armazenar os parâmetros, é necessário, no máximo,  $|\log_2(n_x)| + 1$ .

Para aplicar aos sinais de entrada não normalizados, o fator de esparsidade  $\alpha$  na Figura 2.13 deve ser ajustado de acordo com cada sinal de entrada inteiro  $\mathbf{x}_{int}$ . Esse ajuste não afeta a acurácia da classificação, conforme demonstrado em [16] [3].

O Algoritmo 2 mostra os procedimentos para implementar o classificador LAST com as técnicas xQuant em tempo de execução.

#### **Algorithm 2** Algoritmo LAST com as técnicas xQuant

```

1: procedure LAST

// Carrega D, w, e X

D \leftarrow Carrega\ dicionario\ D\ xQuant

3:

X \leftarrow Carrega\ imagem

4:

5:

w \leftarrow Carrega\ vetor\ classificador

6:

// Calcula norma do sinal

7:

m_{sum} \leftarrow 0

8:

m_{sum} \leftarrow X_{int}[i][k] * X_{int}[i][k]

9:

norm \leftarrow sqrt(m_{sum}) * alpha\_factor

10:

11:

12:

//Extração de características

if D[k][j] > 0 then

13:

accum + = X_{int}[i][k] \ll D[k][j]

14:

else

15:

accum-=X_{int}[i][k]<<-D[k][j]

16:

17:

//Aplica limiar: max(0,d*x - norm)

18:

19:

f_{\alpha} \leftarrow accum - norm

if f_{\alpha} < 0 then

20:

f_{\alpha} \leftarrow 0

21:

22:

23:

//Aplica a classificação

24:

c \leftarrow w * f_{\alpha}

if c >= 0 then

25:

labels \leftarrow 1

26:

27:

else

labels \leftarrow -1

28:

29:

```

## Capítulo 3

# Implementação do Classificador LAST em um Sistema Embarcado

Nesse capítulo será apresentado como foi feita a implementação do classificador LAST e as técnicas de otimizações utilizadas em *software* e *hardware*, detalhando o uso da síntese em alto nível no processo de projeto para agilizar o desenvolvimento.

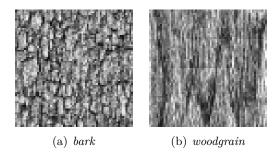

#### 3.1 Bases de Dados Utilizadas

O problema de classificação consistiu na discriminação de 2.000 retalhos extraídos das imagens mostradas na Figura 3.1. Estas imagens são do conjunto de dados Brodatz [43] e também foram utilizados em [36] [3] [16]. A classificação consiste em, a partir de um retalho da imagem, o classificador discerni a qual imagem esse retalho pertence. A construção do conjunto de dados foi realizada como se segue. Em primeiro lugar, dividiu-se cada imagem em duas metades e foi reservada a metade direita de cada imagem para construir o conjunto de treinamento e as metades esquerdas para construir o conjunto de teste. Do conjunto de imagens contidas na metade direita, foram extraídos 1.000 retalhos aleatórios de  $6 \times 6$  pixels e descritos como vetores de 36 elementos que foram normalizados utilizando uma norma  $\ell_2$  igual a 1. O mesmo procedimento foi seguido para construir o conjunto de teste das metades esquerdas.

Figura 3.1: Texturas utilizadas para gerar o *data base*. Essas imagens foram extraídas da base de dados Brodatz [43].

### 3.2 Implementação

Conforme já mencionado, o objetivo desse trabalho é analisar os impactos em um algoritmo de classificação implementado em hardware após ser utilizado as técnicas de redução de custo apresentado em [3]. Diferentemente de [36] [3] [16], onde cada retalho tinha  $12 \times 12$  pixels, optouse por reduzir o tamanho do problema a retalhos de  $6 \times 6$  pixels, a fim de acelerar o desenvolvimento em FPGA. Essa decisão foi motivada pelo uso de um algoritmo simples de multiplicação de matrizmatriz, em vez de os mais complexos como o particionamento de bloco e Strassen [42], conforme foi citado na Seção 2.3. Em aplicações reais, é definitivamente melhor para implementar um algoritmo mais eficiente e/ou genérico que permite acelerar a multiplicação de matrizes, com tamanhos flexíveis.

A implementação fez uso de três ferramentas da Xilinx utilizadas para o desenvolvimento de um SoC.

- Vivado HLS Utilizado para fazer a síntese em alto nível do classificador e gerar um bloco IP desse módulo;

- Vivado Integrar os módulos IP com o processador ARM e fazer a síntese do projeto;

- SDK SoC Utilizado para programar o processador ARM.

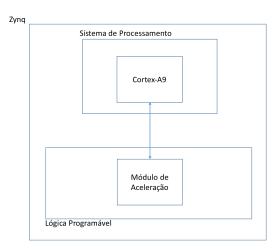

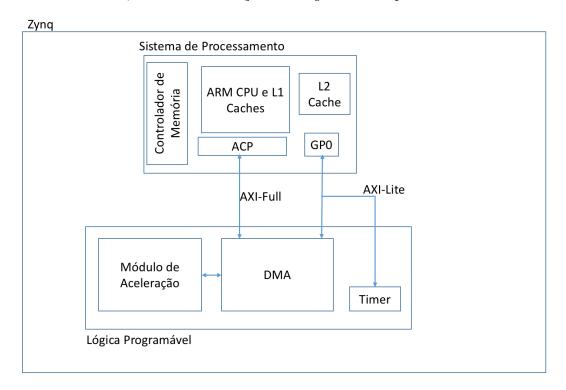

Esse projeto faz uso de um processador ARM e uma FPGA, logo decidiu-se em implementar em hardware as operações mais custosas, as que demandam maior tempo de processamento, ou seja, a multiplicação matriz-vetor, juntamente com a aplicação da função de ativação de retificadora, onde todo valor menor que zero é forçado a ser zero e o processador é responsável pelo restante da classificação retornando a classe prevista, sendo que o processador é o controlador do sistema, o qual gerencia o módulo implementado em hardware. O diagrama da Fig. 3.2 mostra o sistema implementado.

Figura 3.2: Diagrama da solução Implementada, utilizando o barramento AXI-Lite. O bloco de aceleração é representado como um módulo IP, sendo que esse módulo pode ser o  $Floating\ Point$  - Fp ou o IP xQuant- xQ.

Nessa primeira implementação não foi utilizado um barramento de alto desempenho, logo a comunicação foi feita através do barramento AXI-Lite, onde é possível enviar apenas um dado por transação. Para a segunda implementação utilisou-se um barramento de alta performance, AXI-Full, juntamente com a interfaces ACP, possibilitando extrair o melhor desempenho das otimizações aplicadas em hardware. O diagrama da Fig. 3.3 mostra o sistema implementado otimizado para transferência de dados.

Figura 3.3: Diagrama da solução Implementada. O bloco de aceleração é representado como um módulo IP, sendo que esse módulo pode ser o Floating Point - Fp ou o IP xQuant- xQ

Como o foco deste trabalho foi a análise de uso de recursos na FPGA, foi somente utilizada a parte de pós-processamento da técnica xQuant, ou seja, não se utilizou a técnica que encontra a melhor aproximação para a acurácia do classificador original. Portanto, treinou-se  $\mathbf{D}$  e  $\mathbf{w}$ , com 10 neurônios para o conjunto de treinamento usando o algoritmo LAST original com as configurações descritas em [36]. Em seguida, foi aplicada as técnicas xQuant como pós-processamento descritos na Seção 2.4 para  $\mathbf{D}$ , obtendo a sua versão quantizada  $\mathbf{D}_{xQuant}$ . A partir de agora, utiliza-se  $(\mathbf{D}, \mathbf{w})$  para se referir ao classificador original LAST e  $(\mathbf{D}, \mathbf{w})_{xQuant}$  para se referir a sua versão quantizada obtida usando xQuant.

### 3.3 Implementação em Software

Usando a Equação 2.4, primeiramente foi implementado o classificador original  $(\mathbf{D}, \mathbf{w})$  em C para ser executado em *bare metal*, isto é, sem nenhum sistema operacional, e utilizou-se ponto flutuante de 32 *bits* definido pelo padrão IEEE-754. Em seguida, buscou-se otimizar o código, utilizando na compilação a flag de otimização "O3", para que o compilador pudesse usar as melhores estratégias de otimização de código, como desenrolar de *loop*, função *inline* automática e código de reordenação e particionamento.

A implementação em *software* foi utilizada como modelo referência nas comparações posteriormente apresentadas nesse trabalho. A partir desse modelo foi feito o estudo computacional, avaliando as operações mais custosas de executar no processador e iniciou-se a implementação de módulos de aceleração feitos em *hardware* utilizando a ferramenta de síntese em alto nível desenvolvida pela *Xilinx*.

### 3.4 High Level Synthesis - HLS

Para a implementação do co-processador em *hardware*, utilizou-se a ferramente de síntese em alto nível (HLS, do inglês *High Level Synthesis*). HLS é uma ferramenta utilizada para realizar síntese em alto nível, ou seja, é uma ferramenta desenvolvida para agilizar o desenvolvimento de projetos. O HLS converte C/C++ em linguagem de *hardware*. Nesse trabalho foi utilizado a ferramenta *Vivado HLS* desenvolvido pelo fabricante *Xilinx*, o qual é compatível com o *kit* de desenvolvimento utilizado, a *Zedboard*.

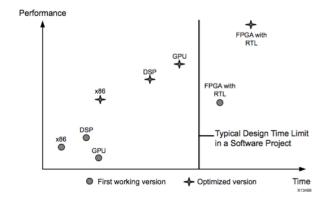

Historicamente o modelo de programação de uma FPGA era RTL (do inglês register-transfer level), esse modelo de programação é análoga a linguagem assembly em engenharia de software, isso significa que o projetista consegue obter bons resultados, mas ao custo de uma alta demanda de tempo para o desenvolvimento. A Figura 3.4 mostra um gráfico de um fluxo de projeto utilizando FPGA com RTL e diferentes plataformas computacionais.

Figura 3.4: Comparativo Tempo vs Performance da aplicação em um projeto [5].

Observando a Figura 3.4 é possível concluir que projetos desenvolvidos em software são realizados relativamente rápido, respeitando a um cronograma típico para desenvolvimento de software, ainda é possível observar que uma solução otimizada feita em software é possível obter melhores resultados e em menos tempo comparado com uma solução feita em FPGA não otimizada. Em [44] os autores fizeram a comparação entre FPGA, GPU e CPU em processamento de imagens para três algoritmos de processamento com diferentes graus de complexidade e dependendo do algoritmo é possível obter resultados de performance de processamento equivalente para as três plataformas, logo o trade-off entre as plataformas se dá pela frequência de operação da GPU (10 vezes superior) e o paralelismo da FPGA, ou seja a quantidade de recursos diponíveis na FPGA para implementar o máximo de operações em paralelo.

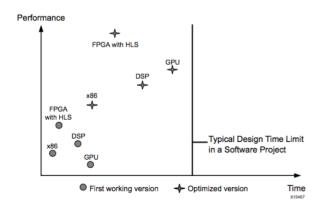

Recentemente com o avanço dos compiladores para realizar síntese em alto nível (HLS), o uso de FPGA em projetos que demandam um menor tempo de desenvolvimento vem se mostrando interessante, apresentando resultados com maior performance e em menos tempo, superior que soluções disponíveis na engenharia de *software*.

A Figura 3.5 mostra o gráfico comparando o tempo de desenvolvimento de um projeto utilizando FPGA com HLS.

Figura 3.5: Comparativo Tempo vs Performance da aplicação em um projeto [5].

Com o uso de ferramentas de síntese em alto nível já começa a ser interessante o uso de soluções heterogênias (CPU+FPGA), já que o tempo de desenvolvimento em FPGA necessário, consegue ser o mesmo comparado com projetos típico para desenvolvimento em *Software*, não necessitando de um cronograma muito extenso.

### 3.5 Implementação em FPGA Utilizando Floating Point

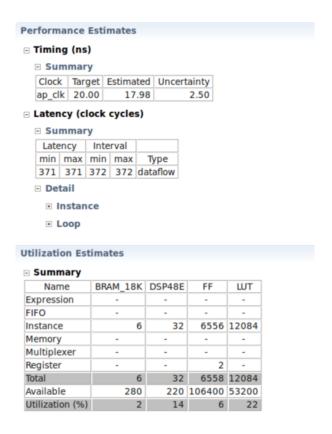

Com a implementação feita em software, Seção 3.3, verificou-se que a operação de multiplicação matriz-vetor, na classificação em tempo de teste, é a que mais demanda recursos computacionais, logo implementou-se um módulo responsável por realizar a multiplicação matriz-vetor e aplicar o limiar, utilizando a ferramenta Vivado HLS. Na primeira implementação o co-processador recebia apenas 1 dado por transação. Utilizando a ferramenta de síntese em alto nível Vivado HLS, criouse o módulo IP para ser utilizado conforme mostrado na Figura 3.2, o Anexo I apresenta como fazer a síntese em alto nível, gerando o módulo IP com o Vivado HLS, também é mostrado como utilizar o Vivado para criar o sistema PS-PL e a síntese do bitstream para configurar a FPGA. É altamente aconselhavel a leitura do Anexo I para um melhor entendimento do processo de projeto SoC utilizando o kit de desenvolvimendo Zedboard.

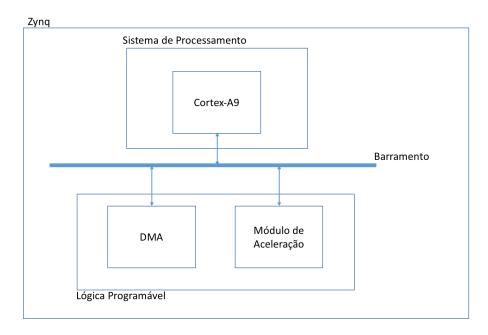

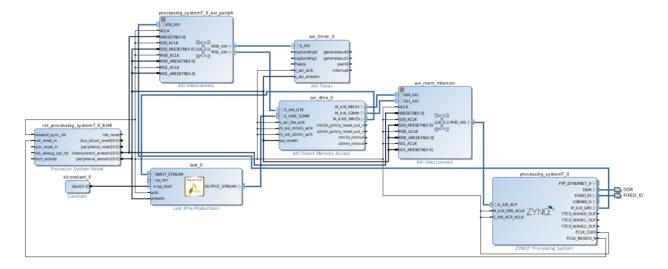

Identificou-se com essa primeira implementação, que a solução não era otimizada, devido a alta latência no envio dos dados, por fornecer um baixo *trhoughput*, portanto decicdiu-se realizar a segunda implementação, Figura 3.6, utilizando interfaces de alta performace para se conectar ao barramento, extraindo um melhor envio/recebimento de dados pelo barramento do módulo de aceleração. Nessa segunda implementação, o co-processador foi capaz de processar um bloco de

vetores 50 de 36 dimensões com valores em ponto flutuante com precisão única (32 bits). Por uma questão de conveniência, nomeou-se a solução Floating Point de Fp.

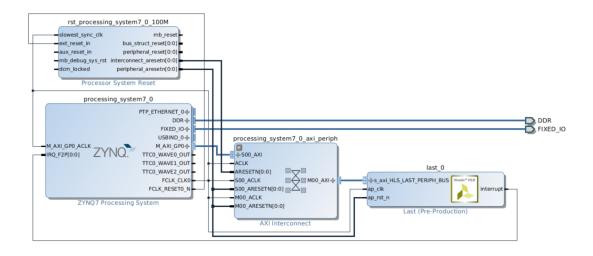

Figura 3.6: Diagrama da solução para implementar módulo Fp. Percebe que o barramento de alta performance o AXI-Full é conectado a interface ACP e a DMA, é por meio desse barramento que trafega os dados de entrada e saída do sistema. O barramento AXI-Lite é utilizado para controle da DMA e do Timer, sendo que esse último foi utilizado para medir o tempo de execução e realizar as comparações de performance do sistema.

Para a implementação do módulo de aceleração, deve-se criar um módulo IP. Para criar o módulo IP utilizou-se a ferramenta de síntese em alto nível Vivado HLS. Para sintetizar o módulo IP, foi necessário criar uma função top level, a qual descreve o comportamento do módulo, essa descrição é feita em C. Então para implementar o classificador em estudo, codificou a multiplicação matriz-vetor e aplicou o limiar. O próximo passo é criar o tipo de interface que o módulo terá. Conforme é visto na Figura 3.6, a comunicação entre a DMA e o módulo IP ocorre através do barramento AXI-Stream. Para criar a interface com essas características fez-se uso das directivas.

As directivas podem ser informadas para o compilador de síntese de alto nível de duas maneiras, a primeira é escrevendo diretamente no código fonte utilizando a assertiva #pragma, a segunda maneira é através de um arquivo de directivas, que o compilador utiliza para inserir as directivas necessárias para a síntese do módulo IP em HLS, logo para criar a interface AXI-Stream, fez uso da directiva #pragma, para criar a interface de entrada e a interface de saída, conforme é visto a seguir:

```

#pragma HLS INTERFACE axis port=in_stream

#pragma HLS INTERFACE axis port=out_stream

```

A próxima etapa foi aplicar as otimizações de hardware. A primeira otimização foi aplicar

a directiva *Dataflow*, com essa otimização foi possível realizar um *pipeline* com as funções de multiplicação a aplicar o limiar. A próxima otimização foi especificamente na multiplicação, onde foi desenrolado parcialmente o *loop* e fez-se o *pipeline*, para mais detalhes ver Anexo II. Com o *top level* criado e com a directivas de otimização aplicadas, sintetizou-se o módulo IP em HLS.

Com o módulo IP sintetizado, iniciou-se a geração do bitstream, arquivo que descreve a configuração para a FPGA, logo a síntese desse arquivo foi feita com a ferramenta de desenvolvimento Vivado 2015. O módulo IP criando anteriormente estará compactado, então, primeiramente foi necessário descompactar os fontes, isso é feito automaticamente através das ferramenta Vivado, necessitando apenas informar onde se localiza o arquivo compactado. Após a ferramenta descompactar o módulo IP, instanciou-se todos os módulos IP necessários para o projeto.

- ZYNQ7 Processing System;

- Módulo IP FP;

- Axi Timer.

Com os módulos instanciados, realizou-se as configurações e o roteamento dos mesmos. O próximo passo é a geração do bitstream, utilizado para configurar o FPGA. Com a finalização da síntese realizada pelo Vivado, exportou-se os arquivos de configuração do hardware e o bitstream para a ferramenta de desenvolvimento SDK Soc, foi nesse ambiente que se desenvolveu o código em C para programar o Zynq em bare-metal, para mais informações dos procedimentos para gerar o bitstream e cross-compilar para o processador, consultar o Anexo III.

### 3.6 Implementação em FPGA Utilizando xQuant