Instituto de Ciências Exatas Departamento de Ciência da Computação

# When Technical Solutions are not Enough: Analysing Challenges at Delivery in Mixed-Signal projects inside Design Houses - Software Engineering Research Perspective

Tiago Pereira Vidigal

Thesis presented as partial requirement for conclusion of Professional Master's Program in Applied Computing

> Advisor Prof. Dr. Carla Silva Rocha Aguiar

> > Brasília 2022

# Ficha catalográfica elaborada automaticamente, com os dados fornecidos pelo(a) autor(a)

PP436w When

Pereira Vidigal, Tiago

When Technical Solutions are not Enough: Analysing

Challenges at Delivery in Mixed-Signal projects inside

Design Houses - Software Engineering Research Perspective /

Tiago Pereira Vidigal; orientador Carla Silva Rocha Aguiar.

-- Brasília, 2022.

182 p.

Dissertação(Mestrado Profissional em Computação Aplicada) - Universidade de Brasília, 2022.

1. Circuitos integrados. 2. Grounded Theory. 3. Perspectiva socio-técnica. I. Silva Rocha Aguiar, Carla, orient. II. Título.

Instituto de Ciências Exatas Departamento de Ciência da Computação

# When Technical Solutions are not Enough: Analysing Challenges at Delivery in Mixed-Signal projects inside Design Houses - Software Engineering Research Perspective

Tiago Pereira Vidigal

Thesis presented as partial requirement for conclusion of Professional Master's Program in Applied Computing

Prof. Dr. Carla Silva Rocha Aguiar (Advisor) FGA/UnB

Prof. Dr. George Marsicano Corrêa Prof. Dr. Renato Coral Sampaio FGA/UnB FGA/UnB FGA/UnB FGA/UnB FGA/UnB FGA/UnB FGA/UnB FGA/UnB FGA/UnB

Prof. Dr. Paulo Roberto Miranda Meirelles  ${\it CMCC/UFABC}$

Prof. Dr. Marcelo Ladeira Coordinator of Postgraduation Program in Applied Computing

Brasília, December 29th, 2022

# Dedicatória

Este trabalho é dedicado a minha família pelo eterno apoio para investir em meus estudos. Em especial a minha esposa que, por sempre estar ao meu lado, me permitiu chegar tão longe em minhas iniciativas acadêmicas, profissionais e pessoais.

# Agradecimentos

Gostaria de agradecer a Chipus Microelectrônica pelo apoio e viabilização desta jornada disponibilizada pela Universidade de Brasília. William Prodanov e Daniel Ferrão foram fundamentais para alinhar este estudo científico com as necessidades da empresa, enquanto a Profa. Dra. Carla Rocha orientou a realização de um diagóstico profundo e estruturado da empresa proporcionando uma tomada de decisão mais embasada e com maior chance de sucesso. Também agradeço pelo apoio do Prof. Dr. George Marsicano, do Prof. Dr. Renato Coral e do Prof. Dr. Paulo Meirelles que permitiram a conclusão do mestrado.

# Resumo

Pesquisas em Engenharia de Software estão evoluindo na analise sócio-técnica e métodos de pesquisa para tratar desafios na indústria. Outros setores de tecnologia que não apresentam tantos trabalhos neste assunto, como circuitos integrados, podem se beneficiar destes estudos. Este trabalho é um caso de estudo para identificar desafios nos processos de entrega entre as disciplinas digital e analógico em projetos de sinais mistos em uma design house específica, considerando perspectivas técnicas e sociais. Nós realizamos 17 entrevistas semi-estruturadas e examinamos os documentos de processos disponíveis, analizando o dado com Teoria Fundamentada Socio-Técnica. Nós mapeamos 14 construtos, 13 proposições e duas explicações para identificar estes desafios enfrentados por times de sinais mistos. Este estudo contribui para a discussão de aspectos sociais em trabalho científicos sobre Semicondutores e apresenta uma lista de possíveis desafios nas entregas no contexto da empresa focada. As causas raiz propostas são os processos de especificação incipientes no contexto de times multidisciplinares e a falta de práticas relacionadas à colaboração em times cross-functional. Estudos sobre Engenharia de Requisitos e DevOps proporcionam reflexões para definir implicações para melhorias na organização.

Palavras-chave: circuitos integrados, teoria fundamentada, cross funcional, sociotécnico, sinais mistos, entrevista semi-estruturada, devops, requisitos

# Abstract

Research on Software Engineering is evolving in the socio-technical analysis and research methods to address the challenges in the industry. Other technology sectors that do not present much research on this topic, like integrated circuits, could benefit from those studies. This work is a case study to identify challenges in delivery processes on mixed-signal projects at a specific design house, considering both technical and social perspectives. We performed 17 semi-structured interviews and examined the available process documents. We analyzed the data using Socio-Technical Grounded Theory. We mapped 14 constructs, 13 propositions, and two explanations to identify those challenges faced by mixed-signal teams. This study discusses the social aspects of Semiconductor's research, and we propose a list of possible delivery challenges in the context of the focal company. The suggested root causes of challenges in mixed signal projects are the incipient processes specification and the lack of practices related to collaboration in cross-functional teams. Requirement Engineering and DevOps studies provide insights into the organization's implications for improvement.

**Keywords:** integrated circuits, grounded theory, cross-functional teams, socio-technical, mixed-signal projects, semi-structured interview, devops, requirement Engineering

# Contents

| 1 | Intr | roduction 1                         |  |  |  |  |  |  |

|---|------|-------------------------------------|--|--|--|--|--|--|

|   | 1.1  | Objective                           |  |  |  |  |  |  |

|   | 1.2  | Contributions                       |  |  |  |  |  |  |

| 2 | Bac  | kground and related works 5         |  |  |  |  |  |  |

|   | 2.1  | Grounded Theory                     |  |  |  |  |  |  |

|   | 2.2  | Grounded Theory main variations     |  |  |  |  |  |  |

|   |      | 2.2.1 Classic/Glaserian GT          |  |  |  |  |  |  |

|   |      | 2.2.2 Strauss-Corbin GT             |  |  |  |  |  |  |

|   |      | 2.2.3 Constructivist GT             |  |  |  |  |  |  |

|   | 2.3  | Socio-Technical Grounded Theory     |  |  |  |  |  |  |

|   | 2.4  | Integrated Circuit Design House     |  |  |  |  |  |  |

|   | 2.5  | Organizational team structures      |  |  |  |  |  |  |

|   | 2.6  | Cross-functional teams              |  |  |  |  |  |  |

|   | 2.7  | Software and IC life cycles         |  |  |  |  |  |  |

|   | 2.8  | Related Works                       |  |  |  |  |  |  |

| 3 | Met  | chodology 17                        |  |  |  |  |  |  |

|   | 3.1  | Methodology justification           |  |  |  |  |  |  |

|   | 3.2  | Focal organization                  |  |  |  |  |  |  |

|   | 3.3  | Methodology description             |  |  |  |  |  |  |

|   |      | 3.3.1 Data Collection               |  |  |  |  |  |  |

|   |      | 3.3.2 Data Analysis                 |  |  |  |  |  |  |

| 4 | Res  | ults 23                             |  |  |  |  |  |  |

|   | 4.1  | Collected information               |  |  |  |  |  |  |

|   | 4.2  | Coding iterations                   |  |  |  |  |  |  |

|   |      | 4.2.1 Method testing iteration      |  |  |  |  |  |  |

|   |      | 4.2.2 Digital perspective iteration |  |  |  |  |  |  |

|   |      | 4.2.3 Analog perspective iteration  |  |  |  |  |  |  |

|     |                      | 4.2.4 Management perspective iteration                           | 33         |

|-----|----------------------|------------------------------------------------------------------|------------|

|     |                      | 4.2.5 Confront of perspectives and refinement iterations         | 34         |

|     | 4.3                  | Coding Results                                                   | 34         |

| 5   | Disc                 | ussion                                                           | 38         |

|     | 5.1                  | Results analysis                                                 | 38         |

|     | 5.2                  | Implications for focal company                                   | 41         |

|     | 5.3                  | Implications for academia                                        | 42         |

|     | 5.4                  | Limitations                                                      | 43         |

| 6   | Con                  | clusion                                                          | 14         |

| Rei | feren                | ces                                                              | 15         |

| An  | nex                  |                                                                  | 17         |

| Ι   | Orig                 | inal interview snippets                                          | 18         |

| II  | Inte                 | rview script                                                     | 52         |

|     | II.1                 | Invitation e-mail (in Portuguese)                                | 52         |

|     | II.2                 | Script                                                           | 53         |

|     |                      | II.2.1 Interview initialization                                  | 53         |

|     |                      | II.2.2 Interview questions                                       | 53         |

| III | $\operatorname{Cod}$ | ing evolution records                                            | 55         |

|     | III.1                | Coding 01: Experimental concepts after first interview           | 55         |

|     | III.2                | Coding 02: Initial concepts                                      | <b>3</b> 4 |

|     | III.3                | Coding 03: Corrupted record of iteration                         | 31         |

|     | III.4                | Coding 04: Iteration after first interviews                      | 36         |

|     | III.5                | Coding 05: First stable concepts from digital perspective        | )5         |

|     | III.6                | Coding 06: First stable concepts from analog perspective         | 30         |

|     | III.7                | Coding 07: First stable concepts from managers perspective 14    | 43         |

|     | III.8                | Coding 08: Crossing digital, analog and managers perspectives 10 | 31         |

# List of Figures

| 2.1 | Socio-Technical Grounded Theory method (from [1])                                     | 10 |

|-----|---------------------------------------------------------------------------------------|----|

| 2.2 | Simplified workflow of a mixed-signal project at Design Houses                        | 11 |

| 2.3 | Simplified representation of Siloed Departments organizational structure              | 12 |

| 2.4 | Simplified representation of DevOps organizational structure                          | 12 |

| 2.5 | Simplified representation of Platform Teams organizational structure                  | 13 |

| 2.6 | Simplified representation of Cross-Functional organizational structure. $\ \ . \ \ .$ | 13 |

| 2 1 | Methodology workflow of this research                                                 | 10 |

| J.1 | Methodology workhow of this research                                                  | 19 |

| 3.2 | Draft of constructs and propositions                                                  | 22 |

| 4.1 | Snippet of highlighted and annotated transcript of the first interview                | 29 |

| 4.2 | Snippet of a code with interpretation and interview parts at the first iteration      | 29 |

| 4.3 | Diagram to record code relationship observed at the first iteration                   | 30 |

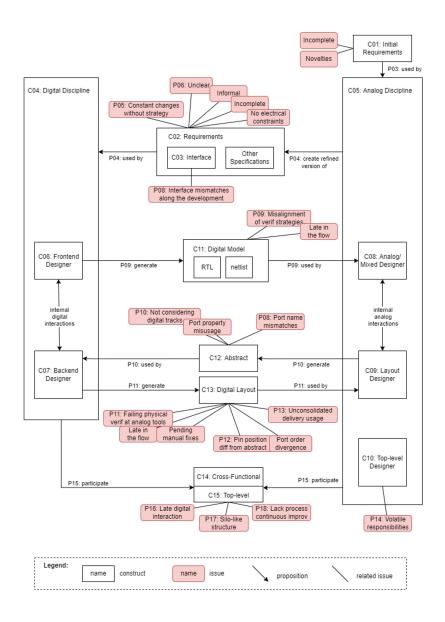

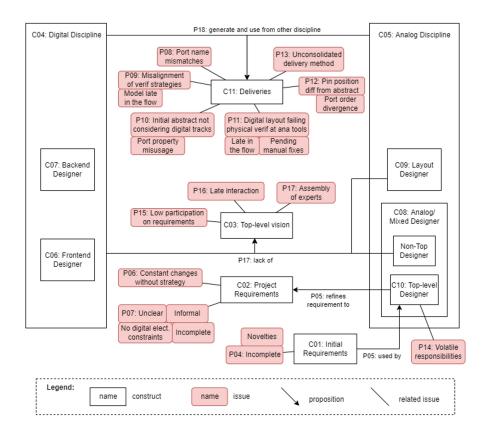

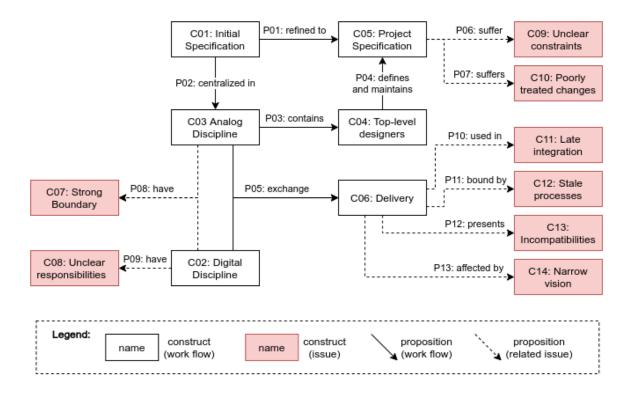

| 4.4 | Conceptual diagram illustrating concepts and relationships regarding deliv-           |    |

|     | ery challenges in the focal company                                                   | 37 |

# List of Tables

| 2.1 | Summarized comparison of key differences between 3 main strands of Grounded |    |

|-----|-----------------------------------------------------------------------------|----|

|     | Theory based on Stol at al. [2]                                             | 9  |

| 4.1 | Interview participants information                                          | 24 |

| 4.2 | Code book of the digital perspective at Iteration $2 \ldots \ldots \ldots$  | 31 |

| 4.3 | Code book of the analog perspective at Iteration 3                          | 32 |

| 4.4 | Code book of the management perspective at Iteration $4$                    | 33 |

| 4.5 | Summary of final iteration of conflict of perspectives                      | 35 |

| 4.6 | Main concepts regarding delivery challenges between digital and analog ex-  |    |

|     | perts on the target IC Design House of the study case                       | 36 |

| 4.7 | Relationships establishing workflow and issue associations between concepts |    |

|     | of delivery challenges at the focal company $\dots$                         | 36 |

| 4.8 | Explanations based on the concepts and relationships discovered on the      |    |

|     | study's scope                                                               | 37 |

# Chapter 1

# Introduction

Software Engineering researchers introduced social aspects in their analysis for a holistic diagnosis of challenges presented in the industry. This socio-technical perspective is not present in studies of other technology sectors, which could further improve the precision of proposed solutions. Semiconductors' system design is one of those sectors that could benefit from existing Software studies adopting this approach.

The semiconductor industry has been in constant growth since the invention of the transistor, and its technology is present in practically all electronic products [3]. Automotive, aerospace, communication, computing and other industries depend on chips to build their products, and those businesses were substantially affected by the 2021 worldwide chip shortage [4]. Integrated Circuits (ICs) are no longer just a group of electronic components but systems inserted into multiple broad and complex contexts.

Electronic circuits are electrical systems with the purpose of processing signals. The integrated circuit technology can implement such systems on silicon chips composed of billions of electronic devices in millimetric areas [5]. Microelectronics evolution resulted in density and performance increases along with cost reduction, enabling solutions at multiple sectors [3]. Complex circuit projects require mapping customer needs and developing, verifying, and validating software models abstracting circuits. Thus, these circuit projects have workflow similar to Software projects.

The complexity of chip projects causes many challenges to delivery in the expected scope, budget, and time. Often in the industry and academic forums, we discuss the integration of Intellectual Properties (IPs) from multiple providers/vendors, different circuit topologies, advanced nodes complexity, distinct power and clock domains, restrictive accuracy or consumption, robustness across Power, Voltage, and Temperature (PVT) variations, and similar challenges. In this study, those represent the **technical aspects** of IC development. It is common to associate these elements as the root cause of project

delivery problems, such as solution incompatibility, schedule delays, and overall high development costs.

Technical challenges comprehend most research regarding integrated circuits. However, a broader view is required for more effective solutions, as can be seen in Software systems where both technological and social aspects enable a complete analysis [6]. This rationale leverages a deeper understanding of system projects and related variables, improving their success rate. Social aspects like collaboration, coordination and formation of individuals can ponder the analysis of socio-technical phenomenons [1]. In this study, the **social aspects** considered are the relationship between members through organizational structures while human aspects and values are not contemplated.

An effective team dynamic [7] together with well-suited processes increase the chances of delivery under the expected cost, scope, and time. Software Engineering scientific studies are broadening their scope from technical to Social-Technical systems [6] because neglecting social aspects of these projects, interwoven with technical ones, make an incomplete investigation and understanding [1]. The same approach can benefit IC studies once projects from both sectors present similarities.

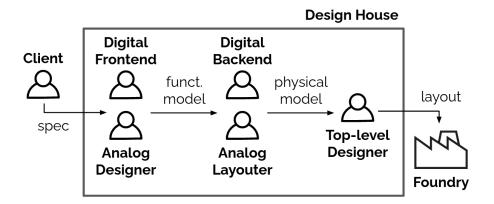

IC Design Houses (DHs) typically receive customer requirements to develop and verify the circuit design at a defined technology for manufacture in a Foundry, sometimes for specific applications or market-oriented. DHs may also perform or enable validation of physical circuits besides taking care of logistics if specified by contract. This supply chain levelled the industry to increase its competency and promoted the development of more complex systems.

The design teams are responsible for modelling circuits in different levels of abstraction, ranging from behavioural to layout, to improve simulation speed [8] and cope with complexity [9]. The engineers responsible for that modelling are usually specialists in one of the two disciplines of integrated circuits: analog or digital. Chips can be of either type or mixed-signal when both are present on a single system.

Mixed-signal projects require deliveries from team members of different technical knowledge. Digital and analog experts work together towards a shared goal while managing the specificities of each discipline and integrating work products from both areas. This team configuration seems to be equivalent to the concept of cross-functional teams [7, 10, 11, 12, 13] which was used in this study to analyze mixed-signal IC teams.

Cross-functional teams in multiple sectors present similar challenges. Some are related to functional affiliation problems [7] where discipline tasks are considered more important compared to the product itself and assist a lack of product and context knowledge among experts [11]. Others are enabled by functional deference [7], which increases the distance between disciplines, reducing common interdisciplinary understanding (or shared under-

standing), clarity of responsibility, and communication or feedback channels [11]. As a result, mixed-signal teams may suffer from similar challenges.

## 1.1 Objective

This research is a case study [14] of a single IC Design House (DH) intending to map the challenges occurring in delivery processes between two technical disciplines, digital and analog. Semi-structured interviews and company documents analysis allowed the authors to collect unstructured data, and we use Socio-Technical Grounded Theory [1] to analyze the data.

The following research questions guided the study:

- RQ1: Which challenges are present in delivery processes of mixed-signal project in Digital Houses?

- RQ2: Why did the delivery challenges between disciplines on the target DH occur?

The focal organization of this study is a small private Semiconductor IC DH with 50 employees and two technical groups: design and validation. The design group has digital and analog departments with a pre-silicon focus, mainly acting before manufacture. The validation group has a post-silicon focus, performing tests on physical chips.

A total of 17 interviews were made, along with an analysis of available documents regarding the company processes. The results are composed of 14 constructs and 13 propositions discovered, leading to 2 explanations defined by the authors: a lack of shared vision between disciplines and incipient specification processes.

## 1.2 Contributions

The main contributions of this work are:

- Analysis of IC design delivery problems from a social-technical perspective;

- A list of delivery challenges between digital and analog disciplines of the focal DH and implications for it;

- A demonstration of the suitability of cross-functional concepts to increase the literature available for discussions regarding mixed-signal teams;

This work presents in Section 2 the related works and concepts used as background for the study. Section 3.3.2 describes the company's context and the methodology adopted while Section 4.3 presents the results found during execution. Section 5.4 contains an analysis of those results to answer research questions, lists the practical implications for the organization and academia, and discloses limitations that bound the authors' conclusion in Section 6.

# Chapter 2

# Background and related works

The research requires an understanding of the company context and a theory basis formulated with related works and concepts used throughout this work. This section presents those topics to clarify the background of the research and illustrate the chip life cycle considered.

The author did not perform an in-depth initial literature review regarding teams, product life cycle and related works to avoid bias, as recommended by the Classic/Glaserian Grounded Theory [2]. The referenced studies below helped the coding refinement iteration and do not represent an extensive analysis of those topics.

## 2.1 Grounded Theory

The Grounded Theory caused a significant impact in sociology research by proposing the application of qualitative methods through data collection techniques to emerge theories from discovered concepts [1]. The creation of variants of the original methodology happened over the years, but some core features are present throughout them. Some of those features are described below based on Stol et al [2].

Literature review in the Grounded Theory context has an interesting trade-off: it provides background and sensitivity regarding the object of study, but it may create bias on the emerging theory. Authors should **limited exposure to literature**: avoid a thorough review of existing literature to promote open-mindedness, avoid confirmation bias, and prevent using existing concepts and theories. This concern does not mean avoiding literature research but must be timed and treated correctly to reduce the undesired influence.

Grounded Theory proposes qualitative methods to develop the theory [1], but this does not mean that researchers may only use qualitative data during the study. The researcher should **treat everything as data**: use all available resources to extract information,

which includes quantitative and qualitative data in any format (text, image, structured, unstructured and others). Other works using GT show the use of interviews [7, 15, 16, 17], formal observation and workshop [7, 15], code and project tracking metrics [16], performance indicators for statistical analysis [15], and emails [16].

Theory and author mature along the execution of the research, so **immediate and continuous data analysis** is relevant to achieve better results. An iterative approach of simultaneously collecting and analysing data enables collection adjustments to increase its effectiveness. Continuous analysis encourages a deep dive into each new information and improves the authors' understanding of the object of study. The immediate analysis is also relevant to keep the context close to the obtained data.

The simultaneous data collection and analysis gradually increment the theory under construction and broadens the understanding of the study target. Throughout the research execution, authors may detect gaps in the planned methodology that compromise the generalization of the results. **Theoretical sampling** is the iterative identification and exploration of those gaps to improve the robustness of emerging theory.

The data analysis objective in Grounded Theory is to discover concepts related to the object of study. Codes are terms or expressions relevant to the GT target and represent those concepts. Codes have a relationship with other codes and can be part of a broader concept, which is called a category. **Coding** is the extraction of those analytical codes and theoretical categories from collected data to structure the emerging theory without considering any codes from previous works.

The data collection can be done by multiple means once "all is data" as stated by Glaser [2]. However, authors often have personal thoughts during collection and analysis that should be considered while building the theory. **Memoing** is the act of taking notes throughout the method execution to aid coding and evidentiate theory gaps that theoretical sampling must address.

Each collected data should not be considered alone. **Constant comparison** of data, memos, codes, and categories is required to evolve coding with a holistic approach. The objective of constant comparison is to adjust concepts until all data collected 'fit' the emerging theory. This approach is similar to manual data mining performed by the researcher.

The theory keeps evolving while data collection and analysis are executed and improved. During the initial steps of the method, the theory might suffer drastic changes because acquired information is bound to be novel in the study context. As the research continues, the probability of new information drops and emerging theory changes are subtle. This point is the **theoretical saturation** where emerging theory is mature and does not present significant changes with new data. The saturation indicates the theory

conclusion, and the researcher can stop the method.

## 2.2 Grounded Theory main variations

Multiple variations derived from the original Grounded Theory approach created adaptations with different philosophical backgrounds and considerations. However, not all studies use GT correctly or explain the variation and adaptions used in the methodology [2, 1]. Authors are encouraged to know existing variations and guidelines for more effective usage of the method.

The main strands of GT are: Classic/Glaserian, Strauss-Corbin and Constructivist [2]. While all of them follow the common characteristics mentioned in Section 2.1, each has adaptations and characteristics that slightly change the method behaviour. A brief description of each variant is presented below based on Stol et al. and illustrated in Table 2.1.

### 2.2.1 Classic/Glaserian GT

The Classic or Glaserian version of GT has an Objectivist philosophical influence and defends that there is a single and correct description of reality that must be discovered. The research should start within an area of interest, but specific research questions should emerge along the execution of the method to avoid forcing the direction of the theory.

The literature review should be limited and delayed until theory starts to emerge. The initial study can consult works from other areas to increase the theoretical sensitivity of the researcher, otherwise, authors should restrict themselves to avoid influences from previously existing concepts.

The resulting theory should fit the obtained information (codes and categories are adequate for all collected data) and work (it explains or predicts the analysed phenomena). The theory must also be relevant for the study area and modifiable if new data appears.

#### 2.2.2 Strauss-Corbin GT

The Strauss-Corbin version of GT has a pragmatic and symbolic interactionist philosophical influence and defends the construction depending on reflexive interactions between actors and the world. The research can start with broad open-ended research questions and even from some initial literature review.

The author can consult literature throughout the project as a secondary data source to provide concepts and ideas to the emerging theory and increase theoretical sensitivity. Other studies can also aid the formulation of questions for data collection and analysis and provide suggestions for areas relevant to theoretical sampling.

Predefined criteria evaluate the resulting theory to check its suitability. Corbin & Strauss [18] bring a list of considerations that should be used to check the performed research quality. Those points are listed below.

- 1. Fit: How well the findings fit professionals' and participants' experience

- 2. Applicability: How well findings support predictions and decisions

- 3. Concepts: How meaningful, dense and flexible are the findings

- 4. Contextualization of concepts: How clear is the context of the findings

- 5. Logic: How reasonable and clear the findings and methodological decisions are

- 6. Depth: How rich and complete the detailed description of the found concepts are

- 7. Variation: How generic the findings are for application out of the studies scope

- 8. Creativity: How novel and flexible the findings are

- 9. Sensitivity: How clear the researchers drove results based on participants and data

- 10. Evidence of memos: How evident memos created throughout the research are

#### 2.2.3 Constructivist GT

The Constructivist version of GT has a social constructivism philosophical influence [2]. It defends that individual and collective actions construct reality, and observers are not neutral. The research starts by defining initial research questions, which evolve during execution.

The author should not avoid literature review in the early stages but must tailor it to fit the study's purpose. The planned tailoring must simultaneously avoid concept creation bias and increase author sensitivity to the object of study's area.

The resulting theory is valid if it is credible, original, reasonable and useful. Credibility is related to theoretical saturation and instigates the author to evaluate if enough data supports the findings. Originality, reasonability and usefulness considerations are similar to Strauss-Corbin's creativity, logic and applicability criteria.

## 2.3 Socio-Technical Grounded Theory

Traditional GT originated from sociology and, for proper usage in a software engineering context, requires adaptations and guidelines to improve the effectiveness and avoid bad us-

Table 2.1: Summarized comparison of key differences between 3 main strands of Grounded Theory based on Stol at al. [2].

| Element                 | Classic/Glaserian                                                 | Strauss-Corbin                              | Constructivist                                        |

|-------------------------|-------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------|

| Philosophical influence | Objectivism                                                       | Pragmatic & symbolic interactionism         | Constructivism                                        |

| Research questions      | Undefined at start,<br>discovered during the<br>project execution | Broad and open-ended at project start       | Define at start, refined during the project execution |

| Literature review       | Limited until theory starts to emerge                             | During execution as a secondary data source | Tailor to fit study's purpose since start             |

| Evaluation              | Fit the obtained data, work, relevant and modifiable              | Predefined criteria to check suitability    | Credible, original, reasonable and useful             |

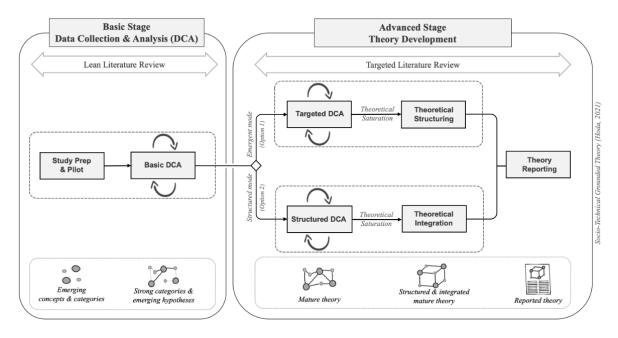

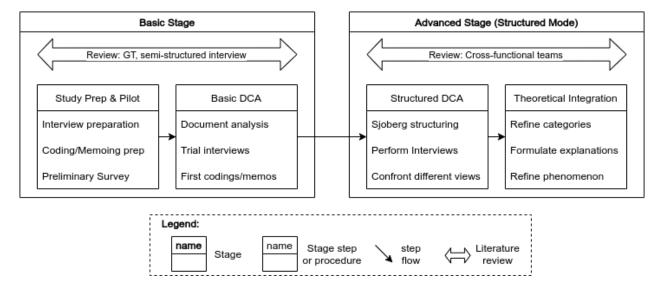

age of the methodology. That resulted in the Social-Technical Grounded Theory (STGT) [1], another variation of the original approach. This alternative method is illustrated in Figure 2.1.

STGT is divided into Basic and Advanced stages. The first stage comprises a lean literature review and basic Data Collection and Analysis (DCA) for preliminary results. This is done to discover emerging concepts and categories, along with the formulation of an initial hypothesis [1].

The last stage of STGT has the objective of collecting from target data sources and types to improve theory incrementally (Theoretical sampling) until it becomes robust and does not change much with new data (Theoretical saturation). Depending on the initial study outcomes, it can be performed either through an emerging or structured mode. Emerging mode is used for a broad phenomenon that presented no clear structure after the Basic stage, while Structural Mode is used for narrower phenomena with clear categories and some theoretical structure already visible after the first stage [1].

STGT Emerging mode requires Targeted DCA to fill gaps and strengthen categories before theory building. After saturation, Theoretical Structuring must be performed to identify the most fitting theory genre or map emergent theoretical structure into pre-existent templates [1].

STGT Structural mode requires Structured DCA where structured coding and constant comparison are performed to guide the theory refinement. Finally, Theoretical Integration will guarantee everything is connected and "makes sense", making clear what

Figure 2.1: Socio-Technical Grounded Theory method (from [1]).

the theory is about and what phenomenon is captured and explained [1].

## 2.4 Integrated Circuit Design House

The Integrated Circuit rising complexity and manufacturing process cost instigated the industry to restructure, dividing circuit design and fabrication into separate organizations [3]. The "fabless" business model represented by organizations called Design Houses outsources all manufacturing of ICs to specialized factories known as Foundries, similar to a software development company outsourcing product operations using cloud platforms.

Mixed-signal circuit design workflow differs among organizations and even between projects inside the same Design House. The major steps comprise the definition of specifications to generate requirements for digital frontend and analog designer experts that will develop a functional model in the form of software in Hardware Description Language (HDL) or circuit schematics. This model is used as a base by digital backend and analog layout experts to generate a physical model, which is integrated and verified by top-level designers before sending a final layout to the Foundry for manufacturing. This flow is depicted at Figure 2.2.

IC projects require consistency between models to be continuously verified [9] but mixed-signal projects, as seen in Figure 2.2, have the additional challenge of integrating models from both disciplines in the project. This interdisciplinarity indicates that tools

Figure 2.2: Simplified workflow of a mixed-signal project at Design Houses.

and methodology are required [9] as well as interpersonal considerations related to the interaction of experts from different specialities.

An unstructured literature search for electronic circuit scientific works related to team interaction and mixed-signal processes provided insights for workflow analysis on such projects. Three databases were used (Scopus, Springer Link and IEEEXplore) with multiple search strings initially containing terms like "mixed-signal", "challenges", "team", "process", "workflow" and "methodology". No work discussing such points was found and it was decided to use studies from the software engineering community to obtain more information.

## 2.5 Organizational team structures

Organizational team structure depicts how the teams, department units, and other organizational entities, are organized, as well as how they relate to each other, implying the lines of communication and hierarchies [19]. According to Conway's law [20] "Organizations which design systems ... are constrained to produce designs which are copies of the communication structures of these organizations".

The effective execution of company processes requires a compatible organizational structure, which in the context of software is the differentiation and integration of operations activities among development and operations groups [21]. Considering Software teams, we can observe 4 common structures: siloed departments, classical DevOps, platform teams and cross-functional teams. This is not a comprehensive analysis but the ones considered for nomenclature purposes only during refinement iterations of coding described in Chapter 4.3.

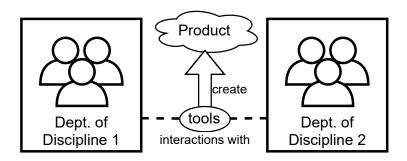

Siloed Departments organizational structure, illustrated at Figure 2.3, presents a clear separation of developers and infrastructure operators [21]. Their roles are well-defined and

differentiated, with each department guided by its own interests. Developers have minimal awareness regarding production and often neglect non-functional requirements, while operators have low influence in the development process. This type of structure invests in tool adoption instead of communication and collaboration among teams. Those companies show limited DevOps initiatives and reduced probability of high delivery performance.

Figure 2.3: Simplified representation of Siloed Departments organizational structure.

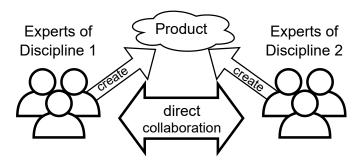

Classical DevOps organizational structure, illustrated at Figure 2.4, focus on the collaboration between developers and infrastructure team [21]. Roles are well-defined and conflicts still remain, but the culture of collaboration reduces task responsibility conflicts and promotes discussion about non-functional requirements across the entire team. However, operators present high levels of stress and must have coding skills. Once alignment of different departments is necessary and very complex, high delivery performance is limited in this type of team.

Figure 2.4: Simplified representation of DevOps organizational structure

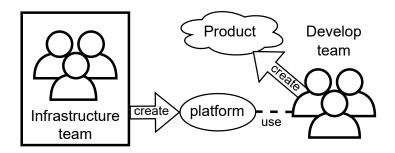

Platform Teams organizational structure, illustrated in Figure 2.5, has an infrastructure team as developers of a highly automated infrastructure services platform to allow deployment by developers (their clients) [21]. Communication is usually limited to solving incidents, and the product team becomes fully accountable for non-functional requirements. Each project often has particular requirements, and infrastructure team members

are usually present in the team. This cloud-like approach promotes a high delivery performance but is only suitable for larger companies.

Figure 2.5: Simplified representation of Platform Teams organizational structure.

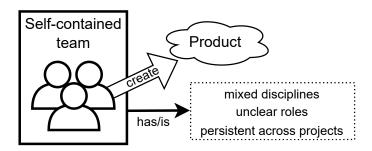

Cross-functional organizational structure, illustrated at Figure 2.6, brings the idea of self-contained independent teams with no clear division among members [21]. It is challenging to guarantee team has all the necessary skills, and the independence of each team may lead to misalignment between them. However, they do not show the idleness of specialists once they are not responsible only for their field. This structure is present in smaller companies and does not provide a strong relationship with high delivery performance. We will detail cross-functional teams because of their similarities with DHs context.

Figure 2.6: Simplified representation of Cross-Functional organizational structure.

## 2.6 Cross-functional teams

Cross-functional teams (also known as multidisciplinary, interdisciplinary, or complementary teams) are considered groups of experts across different disciplines of knowledge that work together for a common goal. This type of team is present in multiple sectors like software [7], aerospace [10], automotive [11], biochemical [12] and health [13]. This concept

seems compatible with mixed-signal IC teams, so the unstructured literature search was refined by adding to the search string the terms "cross-functional" and synonyms. Still, no study discussing this topic in the context of the circuit was found, requiring further analysis to explore the extent of such compatibility.

Cross-functional teams can be classified according to the Organizational Impact Model created by Fuller and Kruchten [7] using 4 categories: Functional deference, Primary affiliation, Horizon of Interest and Alignment with expectations. Derived categories from them are Team cohesion and Product ownership. Those categories help to define if the team is closer to an Assembly of experts of a True (multidisciplinary) team.

Functional deference is the respectful distance an individual keep from the activities of another expert. When a team member limits its contribution to their particular competency and only focuses on "its job" ignoring the "job of the others", we have strong deference. This hard separation of disciplines or functional groups weakens team cohesion because professionals are not encouraged to fully express what they think and reduce product ownership [7].

Primary affiliation is the individual sense of belonging of the professional towards the function or project team. Strong affiliation to the functional department instead of the team encourages the expert to follow department preferences or approaches instead of what the rest of the team considers best for the project. This compromises team cohesion and product ownership [7].

Horizon of interest is how far in the future experts see themselves as part of the team. The organisational model with functional departments and frequent project reassignment along with inadequate Product Planning processes can shorten the horizon if they fail to make an intrinsic connection of members to the product. This results in a lack of concern about the product's success and low attention to long-term plans, reducing product ownership [7].

Alignment with expectations is how close the managers' perception is to the actual product ownership felt by experts. The Assembly of Experts configuration (strong functional deference, function primary affiliation and short horizon of interest) tends to make professionals less concerned to discuss team structure and scope limitations. This can make managers have a false perception that the team ownership is higher than it is [7].

The Organizational Impact Model have synergy with the challenges in cross-functional teams collected by Liebel et. al. [11]. People-related concerns include poor communication and feedback channels, as well as unclear responsibilities and unconnected abstraction levels used by different members. Knowledge-related concerns include a lack of understating regarding the product, context, and common interdisciplinary aspects, besides insufficient resources for maintaining requirements. Such challenges are compatible with

low team cohesion and product ownership categories.

The delivery challenges in the focal company should be also compatible with categories of the Organizational Impact Model if mixed-signal IC teams can indeed be classified as cross-functional teams. The compatibility of concepts can be verified by raising challenges reported by experts but also by comparing workflow similarities with sectors that are proven to have such interdisciplinary teams.

## 2.7 Software and IC life cycles

Software development teams can be analysed using the cross-functional concept [7] and parallels between software and IC life cycles help to understand if this concept applies to circuits context and which are possible adaptations required to allow this analysis. The life cycle of an integrated circuit product has four cycles: global planning, IC design, prototyping, and IC production [3]. In contrast, software engineering's fundamental activities are specification, development, validation, and evolution [22].

The IC global planning defines initial requirements, general project decisions, and estimations [3], very similar to the software specification fundamental activity [22]. The scope of such requirements in both sectors is usually a system that can be divided into parts to cope with complexity, using different abstraction levels for each and integrating those parts to form the expected product.

The IC design will refine technical decisions and develop a software abstraction of the circuit represented by a design database to be sent to a Foundry [3], similar to software design, development, validation, and evolution fundamental activities without considering the operational processes [22]. This is probably the most distinct aspect of the sectors, once the operational activities in Semiconductors usually require high-cost time-consuming manufacturing processes that are not easily fixed or patched compared to software.

The prototyping and IC production is the fabrication and validation of the physical circuit [3], similar to the same software fundamental activities related to IC design but now exclusively related to operational processes [22]. The high cost and low capability of refactoring on IC (called ECO) limit the iterative approach at this maturity level, which has similarities with the software counterpart but in a more extreme spectrum.

The flow similarities between software project lifecycle and circuit design lifecycle seem to indicate that the cross-functional team concept could be used to analyse IC teams. Other factors may influence such compatibility but are not further analysed in this study. Both team characteristics and process parallels are considered enough to allow the discussion of chip design teams using cross-functional teams' concepts.

#### 2.8 Related Works

The analysis of different types of actors to evaluate the interactions at a given moment at an institution, even using cross-functional concepts as a basis, is not something new. The unstructured literature search performed was not able to map studies about that in the context of integrated circuits, but multiple results from Software Engineering were found and used as references.

Fuller and Kruchten [7] is one of the main references of this study and it identifies organisational conditions that impact cross-functional teams' deep collective understanding for better product development and decision making. The Organizational Impact Model that characterizes such teams was developed using Constructivist (Chamaz) Grounded Theory to analyze 18 teams across 7 software companies. The research also shows that team efficiency is reduced if cohesion and product ownership are weak.

López-Fernández et al. [15] characterized DevOps team structures with a multiple case study using Charmaz's Grounded Theory. A total of 31 multinational software-intensive companies were interviewed, generating DevOps team taxonomies. It was concluded that patterns that presented silos (functional department or cultural separation), low autonomy (dependencies that block progression) and not very frequent communication presented low product ownership and reduced delivery efficiency. Both methodology and results have parallels when analysing integration challenges and are compatible with Organizational Impact Model categories.

Layman et al. [16] analyzed success factors on globally-distributed eXtreme Programming (XP) teams with a case study using Glaser's Grounded Theory. It showed that the constant and quick communication between developers and customers, as well as continuous access to process and product information, allowed success even with informal communication and constant requirement changes. The concepts of team cohesion and product ownership appear in the paper as well and provides another example of team analysis that can be associated with Organizational Impact Model categories.

Hoda and Murugesan [17] bring the perspective of self-organizing teams to discuss challenges on multiple levels: project, team, individual and task. It used Glaser and Strauss's Grounded Theory on 21 participants from 6 software companies and 8 managements challenges were discovered: delayed and changing requirements, senior management sponsorship, achieving cross-functionality, effective estimations, asserting autonomy, self-assignment, lack of assignment criteria and task dependency. A methodology for such identification and challenges reported brings interesting insights to this research.

# Chapter 3

# Methodology

A diagnosis considering both social and technical aspects often requires evaluation of qualitative data. Reproducibility is also fundamental to validate and repeat the proposed process in other contexts. In this section, the theoretical foundation of the methodology and its steps is further explained.

## 3.1 Methodology justification

The intent of mapping "which challenges are present in the delivery process" (RQ1) and "why did the delivery challenges" occur (RQ2) is a suitable scenario for a case study. It is a type of applied research whose goal is to mainly identify "how" or "why" something is currently the way it is, with no intention of modifying it during the investigation [14, 23].

Information will be obtained mainly from the experience of team experts of the institution, which can be done by semi-structured interviews. It is an interview method with a defined protocol [24] using predetermined questions that do not necessarily need to be answered. Their purpose is to guide the conversation, reducing the experience required from the interviewer.

Semi-structured interviews generate non-structured data, which we analyse using Grounded Theory (GT). It is a methodology of qualitative research to derive theories based on concepts discovered from the systematic analysis of non-structured data [18]. Theories are very suitable for case studies [25] and have been used often in the Software Engineering context because of the increasingly relevant and intertwined social aspects presented by such systems [1]. It is worth noticing that **theoretical saturation will not be achieved** in **this study** because only a single organization participates in the research.

## 3.2 Focal organization

The target organization of this study is a small private Semiconductor Design House with 50 employees. The Sales sector has a marketing and business view, prospects projects, and collects initial specifications from stakeholders. The Technical sector focuses on project execution and comprises three groups: digital, analog, and hardware specialists.

Digital and analog groups are responsible for their respective disciplines before manufacturing the chip, and they require strong interaction for successful integration. The hardware specialists receive the physical circuit and validate that the behaviour matches the design intent.

Projects start with the Sales sector sending the specification from the client to the Technical sector in the format of a slide presentation. The assigned project manager and leading designers analyse the received document(s) and create an initial plan of tasks, schedule, and stakeholders. Ongoing and to-do activities are recorded and monitored with a project management tool with a process closer to a traditional methodology.

The organization has documented standard processes, a valuable source of information about how it operates. There is no defined quality management team, and the project manager usually handles assurance, monitoring, and control activities in *ad hoc* manner.

The digital and analog disciplines separate specialists according to their expertise. The relationship between them is friendly, but each has its processes, tools, and managers. The company started as a pure analog IC company, and afterwards, a digital team was created to respond to project demands. The analog team was around four times bigger than the digital team during the execution of this research.

The expected relationship between the technical disciplines of the organization is on mixed-signal projects where the analog discipline acts as the central team, and the digital discipline provides support circuits to be integrated. This analog-on-top approach is the standard scenario at the company, and analog members iteratively refine requirements from the initial specification given by the client. Informal channels are the form of communication, but tickets in the project management software register most demands besides information checks.

## 3.3 Methodology description

The methodology adopted in this work is illustrated in Figure 3.1. The basic stage dedicates to a deeper understanding of GT and interview protocols while performing the first data collection and analysis on documents and initial semi-structured interviews. The advanced stage targeted the study to cross-functional teams while doing interviews with

selected team members and confronting the views from each discipline to build a list of integration challenges.

Figure 3.1: Methodology workflow of this research

#### 3.3.1 Data Collection

Four sources are available for data collection: the standard processes documents, managers, digital designers, and analog designers. After each interview or document, a summary with personal comments was recorded (memoing), followed by a mandatory analysis to generate some draft results (iterative analysis).

The process documents are valuable for understanding the project flow regarding digital and analog integration in a company. The data collection of project-related documents aims to list all standardized interactions and risks at the Digital-Analog interface. It is worth noticing that those documents did not provide information regarding mixed-signal activities during the execution of data collection, which caused adaptations in our methodology for a deeper analysis of other sources.

The employees are the primary data sources, and the semi-structured interview process was the focus of theoretical sampling. After the first interviews, more analog layout specialists and managers were included because of low initial representativeness and availability during the execution.

Managers and designers were invited by email to participate in individual online recorded interviews. If agreed, the recording was transcribed while removing identifiable information and the text was stored on a page with ID, data, focus (digital, analog, or management) and additional employee data as in excerpt 1 (data unrelated to any participant).

#### GT excerpt 1

Interview 00 - Digital 00 (13/01/2023)

Genre: Female

Age: 33

Experience: 5 years

Time in company: 3 years

<transcribed and treated text>

### 3.3.2 Data Analysis

The theoretical sampling of data is done iteratively and refined at each collection using memos and diagrams. The iterations are performed first by brainstorming to define a coding of the raw data (open coding), followed by determining the relationship between concepts (axial coding) [18]. During Advanced Stage, the structure described by Sjoberg et al. [25] was used while following STGT guidelines [1].

The first analysis made on each treated interview transcript is a brainstorming to open up it as much as possible to explore all potential information from it. Initially, the text is fully read, highlighting interesting parts and creating side notes with the author's thoughts. This is exemplified in the translated excerpt 2.

#### GT excerpt 2

The main problem with specification is that the information usually comes at the last minute and ends up creating a hurry to run the entire flow. The big problem has been the relationship timing between teams. [...] blocks that we asked for are not complex, and the big problem is those requirements at the last minute.

Author: Commonly, the client is not sure about spec on project start. Everything passing first by analog designers delays even more

Author: Team members are not synchronized

The brainstorm results incremented coding done on previous iterations. New and repeated codes are contrasted using the strategies of comparison flip-flop technique and draw upon personal experience [18]. The resulting constructs [25] were organized each on

a page, grouping concepts and snippets of interviews. An example of constructs from one perspective is excerpt 3 and a construct page content in excerpt 4.

#### GT excerpt 3

Manager perspective constructs

Top-level

Specification

Deliveries

Planning

Cross-functional

Late Actions

Project challenges

#### GT excerpt 4

Manager focus - Specification

Unclear requirements

- \* 01 Manager 01 < interview snippet 1 >

- \* 01 Manager 01 < interview snippet 2 >

- \* 08 Manager 02 < interview snippet 3 >

Expectation alignment (what, how and why)

\* 01 - Manager 01 <<br/>interview snippet 1 >

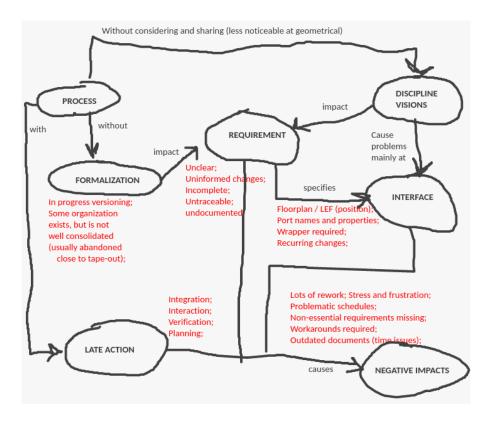

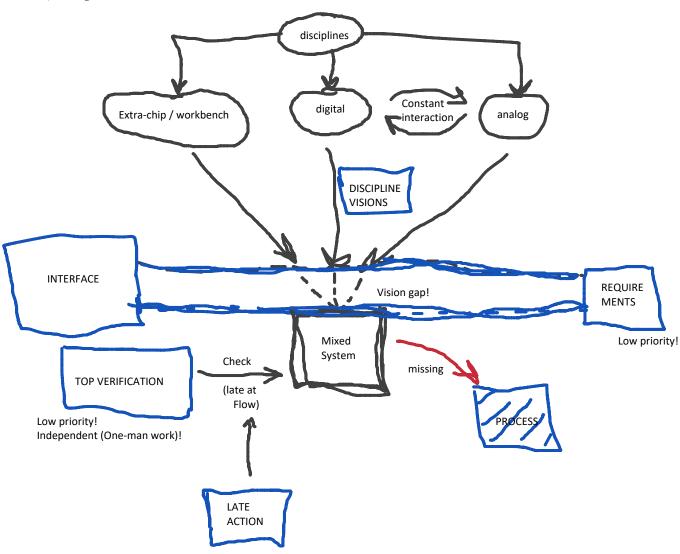

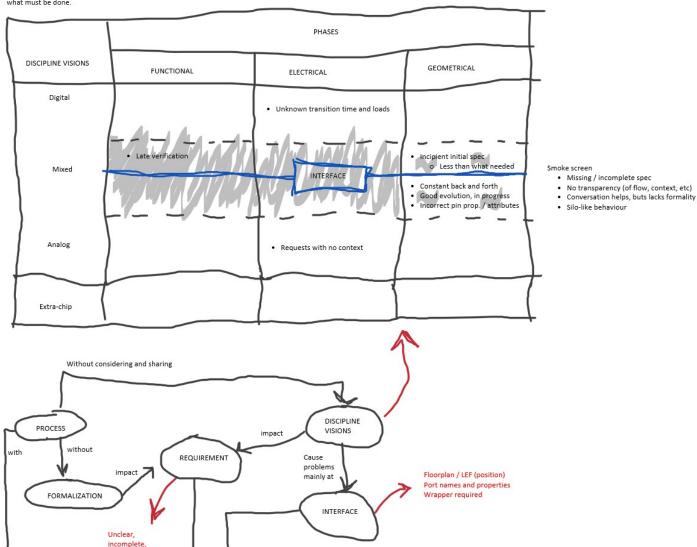

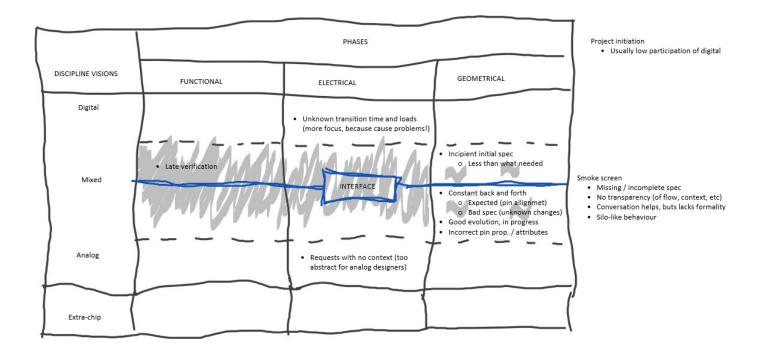

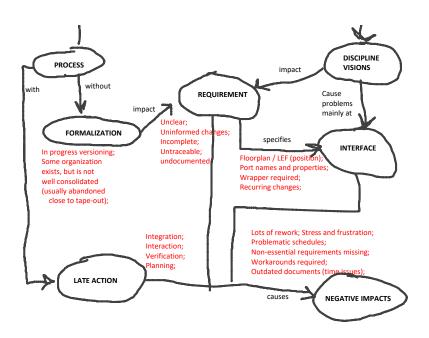

A second step is to crosscut and establish relations with the concepts brainstormed to put data back together [18]. It results in a more structured mapping of causes and consequences, done in parallel with the definition of the constructs. Visual sketches were the main form of recording and improving the relationship between concepts, helping to refine constructs and define propositions [25] relating them. Figure 3.2 shows an example of those intermediary diagrams.

The interview schedule tried to concentrate conversations with employees with similar focuses (digital, analog, and management) as much as possible to perform a "deep dive" in each area. Initially, digital experts were interviewed, followed by analog and managers. Constructs and propositions were created for each focus to create three distinct perspectives confronted to achieve the final coding of this work.

The last analysis step is to interpret the constructs and propositions to formulate explanations. With a scope well defined, this represents the list of main integration

Figure 3.2: Draft of constructs and propositions

challenges generated [25]. The discovered concepts can be illustrated in a diagram to identify the delivery challenges and related factors. The formulated explanations define a possible root cause for the challenges found during the interviews.

# Chapter 4

# Results

The data collection and analysis performed provided information about the distinctive scenario of the company. In this section, the results that provided the constructs and propositions are described, followed by the achieved conceptual diagram and explanations based on them. Supplementary material like complete anonymized interview transcriptions and code book can be found in annexe or at the public repository<sup>1</sup>.

#### 4.1 Collected information

The organization's process standards contain a description of the entire project flow expected in a very high level of abstraction, with separated guidelines for each discipline flow. No document provided information related to technical team interactions, including integrating Digital-Analog subsystems or mixed-signal simulations. There is a strong division of specialists regarding their function and no requirement-related activities exist considering this source.

The interviewee group was composed of five (5) managers and six (6) designers of each discipline (a total of 17). The author made the managers' selection according to their availability, while managers recommended designers according to their experience on mixed-signal projects. The snippets below were translated by the authors once the original interviews were made in Portuguese. The untranslated text of each snippet can be found at Annex I.

The interviews were the main source of information regarding the delivery interactions, mainly for system integration, because of the lack of information about this aspect in the documents. The interviewees' data at Table 4.1 shows that digital designers are older and have more experience, both in academy and industry, compared to analog designers.

https://github.com/tpvidigal/ICDeliveryChallenges.git

However, it is also noticeable that analog designers work in the company longer than digital designers.

Table 4.1: Interview participants information

| Info    | Focus   | Min      | Max    | Mean   | Median  |

|---------|---------|----------|--------|--------|---------|

|         | Digital | 31       | 38     | 35,0   | 35,5    |

| Age     | Analog  | 29       | 34     | 30,5   | 29,5    |

| (years) | Manager | 30       | 45     | 37,0   | 36,5    |

|         | Total   | 29       | 45     | 34,2   | 33      |

|         | Digital | 6        | 14     | 8,5    | 7,5     |

| Sector  | Analog  | 2        | 10     | 6,5    | 7       |

| (years) | Manager | 9        | 20     | 14     | 13      |

|         | Total   | 2        | 20     | 9,4    | 8       |

|         | Digital | 0,5      | 4      | 2,7    | 3       |

| Company | Analog  | 1        | 8      | 4,6    | 4,4     |

| (years) | Manager | 4,3      | 12     | 7,3    | 6,8     |

|         | Total   | 0,5      | 12     | 4,7    | 4,3     |

|         | Focus   | Bachelor | Master | Doctor | Pos-Doc |

|         | Digital | 2        | 4      | 0      | 0       |

| Academy | Analog  | 4        | 2      | 0      | 0       |

|         | Manager | 0        | 4      | 1      | 0       |

|         | Total   | 6        | 10     | 1      | 0       |

The interviews showed deliveries from one discipline to another are known and consistent among designers and managers even if they are not documented. The reported exchanges between disciplines are related to requirements (specification, block symbol, diagrams), abstracts, models (Verilog, schematics) and layouts.

#### Translated interview snippet 1

08 - Manager 02: "There are four deliveries: symbol, abstract, schematic and layout."

The reported general flow is consistent between interviewees, but interaction procedures present slight divergences mainly related to hand-off (versioning and how the artefact is delivered or received). Those known exchanges usually occur in an *ad hoc* manner with no clear process for obtaining deliveries.

#### Translated interview snippet 2

05 - Digital 04: "I also had to get a file from them, but was confusing where to get it and which version of that file was"

There seems to be an overall lack of knowledge regarding the work products generated by the other discipline. The reports about a lack of information on requests (unclear requirements) and verified deliveries that don't work in the other discipline's environment (compilation, DRC or LVS errors) evidence it, with the latter being the most discussed problem throughout the interviews.

#### Translated interview snippet 3

01 - Manager 01: "Because they say 'I know this must be done', 'I know too', 'I know too', but I think it's missing the formalization of that"

#### Translated interview snippet 4

15 - Analog 04: "Sometimes happen to receive digital blocks and, while performing verification using analog tools or opening layout, DRC problems appear"

Not all interaction processes have the same maturity level once delivery issues are often related to requirements, models or layout. The abstract interactions are the most evolved ones with issues related to port name changes, disregard of digital metal tracks, and port properties misusage, indicating some disconnection between disciplines.

#### Translated interview snippet 5

02 - Digital 01: "We evolved significantly on the geometric front... The functional and electrical parts are the bottleneck."

The analog and top-level designers use an initial specification from the client to define an overall architecture, refine requirements, and start implementation. Digital discipline and analog layout activities start only when the project is more mature while requirements continue to be refined.

#### Translated interview snippet 6

03 - Digital 02: "Digital entered much later, started already in dire straits with a very closed specification"

Close to the project's end, digital models and layout are integrated and verified with the analog modules. It caused several schedule delays in the past, mainly late system-level verification activities and layout activities that required integration of digital layout.

#### Translated interview snippet 7

16 - Analog 05: "Many times digital deadline was almost the same as the project deadline, generating excessive work close to the delivery, pulling all-nighters"

Multiple interviewees explained some distance between digital and analog disciplines, calling each other different teams even at the same project. Examples of that were intermediated communication between disciplines through managers, considering digital deliveries as closed unmodifiable IPs and possible cultural baggage of the company.

#### Translated interview snippet 8

01 - Manager 01: "Interface is ... where it reaches the part that you don't know ('I know up to here, I'm working on this room') and the same on the other side, other room... Both stop looking a little before and left a gap"

#### Translated interview snippet 9

05 - Digital 04: "I saw a lot of analog people defining and digital people just follow... Can be just a matter of project flow... Maybe much of the culture from before having a digital team, outsourcing a service"

#### Translated interview snippet 10

10 - Manager 03: "Regarding digital, usually is created a request to them. I don't have penetration on digital team, I don't discuss how digital is made"

#### Translated interview snippet 11

16 - Analog 05: "Many times communication is done with manager as intermediate because he has a vision of both sides. Unlikely both teams talk to each other..."

The first questions of the interview were related to previous and current projects that the interviewee worked on. All designers clearly stated their functions and the name of the projects they participated in. Throughout most interviews, almost no details regarding the developed product were commented with only a few participants, mainly managers and analog designers, giving some insights about them. Layout designers of the analog discipline and digital discipline members especially stated the lack of understanding of the entire system or context of the final product.

### Translated interview snippet 12

11 - Analog 02: "The lack of top vision gets in the way of the project as a whole. If designers don't know the purpose of its block or with whom the block will talk, understanding gets hard "

It is interesting to notice that each group had clear priorities on different aspects of the processes and problems. Digital designers were more concerned with the informality (lack of guidelines or templates) and the incomplete, unclear or unsynchronized requirements (primarily related to the interface).

#### Translated interview snippet 13

04 - Digital 03: "The analog team deliveries are fast but are too verbal.. we often miss track of things."

#### Translated interview snippet 14

07 - Digital 06: "There were things different between abstract and RTL, like port names. Was changed in one place and not changed in another, those changes were not informed."

Analog designers highlighted process topics, mainly the previously mentioned late digital and mixed activities, along with deliveries that work at digital flow and fail at analog flow. An additional concern was the confusing participation of digital discipline, with changing individuals and unclear responsibilities of digital designers.

#### Translated interview snippet 15

09 - Analog 01: "The AMS part too (digital talking with analog), we ended up having only verification on the last days."

#### Translated interview snippet 16

11 - Analog 02: "It wasn't known if digital would be able to do if another person would do... time passes, no one in digital could so have to do the model by myself"

Managers discussed the unclarity and mutability of requirements, even causing rework towards the project end and losing track of information. The lack of synergy between teams was also reported, when communication was good, as stated by designers as well, but not frequent enough or not considering solid points and challenges of the other discipline.

#### Translated interview snippet 17

12 - Manager 04: "We bring and refine requirements while analog part is being designed... But sometimes goes in a hurry and analog designers only give an idea of what they need (later improving it), even being able of creating a formal specification, more detailed"

#### Translated interview snippet 18

13 - Manager 05: "Sometimes I see one team suffers for a long time to do something extremely easy to the other team... This lack of visibility of one side or another ends causing this."

## 4.2 Coding iterations

The author performed data analysis simultaneously with data collection. The processing of interview transcripts followed the methodology described in Section 3.3.2 to generate multiple coding versions presented in the annexe. This section explains how the coding iterations happened and some of the intermediate results obtained.

### 4.2.1 Method testing iteration

The first iteration's objective was to test and adjust the proposed data collection and analysis. A manager volunteered to be interviewed and discuss the process adequacy and result quality. The author performed the interview and transcripted it.

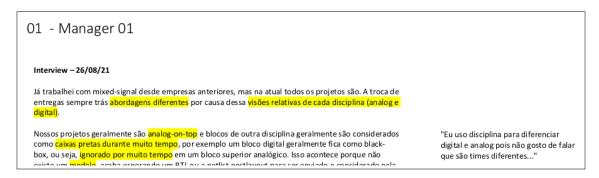

The author read the first interview's transcription while highlighting interesting words or phrases from the conversation. Side notes recorded memos with author reflections or post-interview discussions. Figure 4.1 shows part of the highlighted and annotated transcript of the first interview (in Portuguese).

Figure 4.1: Snippet of highlighted and annotated transcript of the first interview

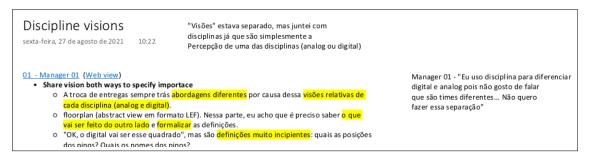

The author chose a word or expression (the code) for each highlighted snippet to represent its main concept. Document pages recorded each code individually with the corresponding text extract, a summarized interpretation of the author and memos as side notes. Codes with existing pages receive additional highlights when related to the latter, which caused "stronger" concepts to have longer pages. Figure 4.2 shows part of the code "Discipline Visions" with interview snippets showing the importance of shared vision between disciplines for specification (partially in Portuguese).

Figure 4.2: Snippet of a code with interpretation and interview parts at the first iteration

Finally, the author created the diagram in Figure 4.3 to record the relationship observed between the initial codes proposed. This visual memo forced the code refinement and helped the result review with the manager.

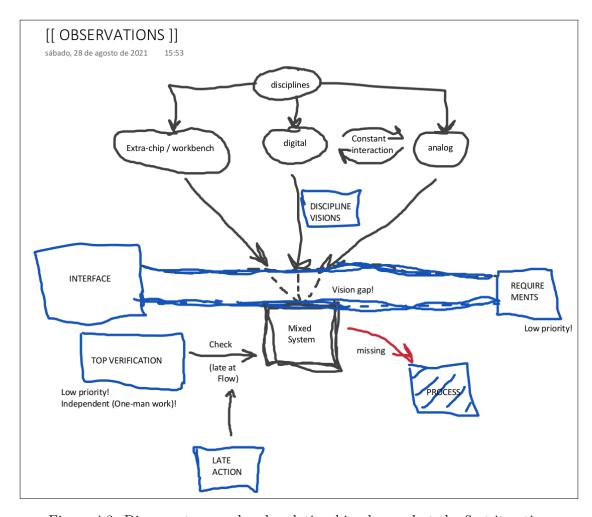

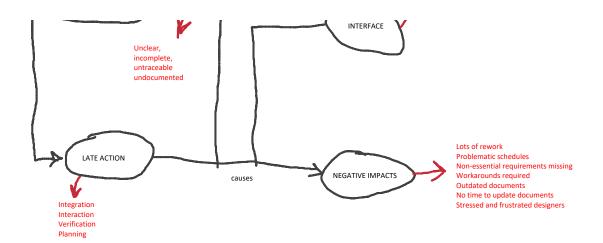

Figure 4.3: Diagram to record code relationship observed at the first iteration

## 4.2.2 Digital perspective iteration

The second iteration's objective was to capture the delivery issues from the digital discipline's perspective. The author repeated the same steps of Iteration 1 for all selected digital designers of the organization. Table 4.2 describes the codes obtained at the iteration's end.

Table 4.2: Code book of the digital perspective at Iteration 2

| Process (workflow-related problems) Interface (system ports related problems) Requirement (specification related problems)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                |                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------|

| Functional (IC behaviour abstraction view)  Electrical (IC netlist and schematics abstraction view)  Geometrical (IC layout abstraction view)  Disciplines (group of people with specific expertise)  Digital (discipline of digital specialists)  Analog (discipline of analog specialists)  Mixed (discipline of mixed-signal specialists)  Extra-chip (discipline of physical chip specialists)  Problems (factors that caused delivery issues)  Informality (non-standardization related problems)  Late action (late interactions or verification problems)  Versioning (traceability and update-related problems)  Information (documentation and team sync related problems)  Process (workflow-related problems)  Interface (system ports related problems)  Requirement (specification related problems) | Codes                                          |                  |

| Electrical (IC netlist and schematics abstraction view) Geometrical (IC layout abstraction view) Disciplines (group of people with specific expertise) Digital (discipline of digital specialists) Analog (discipline of analog specialists) Mixed (discipline of mixed-signal specialists) Extra-chip (discipline of physical chip specialists) Problems (factors that caused delivery issues) Informality (non-standardization related problems) Late action (late interactions or verification problems) Versioning (traceability and update-related problems) Information (documentation and team sync related problems) Process (workflow-related problems) Interface (system ports related problems) Requirement (specification related problems)                                                           | Abstraction levels (delivery views related to  | IC)              |

| Geometrical (IC layout abstraction view) Disciplines (group of people with specific expertise) Digital (discipline of digital specialists) Analog (discipline of analog specialists) Mixed (discipline of mixed-signal specialists) Extra-chip (discipline of physical chip specialists) Problems (factors that caused delivery issues) Informality (non-standardization related problems) Late action (late interactions or verification problems) Versioning (traceability and update-related problems) Information (documentation and team sync related problems) Process (workflow-related problems) Interface (system ports related problems) Requirement (specification related problems)                                                                                                                   | Functional (IC behaviour abstraction view)     |                  |

| Disciplines (group of people with specific expertise) Digital (discipline of digital specialists) Analog (discipline of analog specialists) Mixed (discipline of mixed-signal specialists) Extra-chip (discipline of physical chip specialists) Problems (factors that caused delivery issues) Informality (non-standardization related problems) Late action (late interactions or verification problems) Versioning (traceability and update-related problems) Information (documentation and team sync related problems) Process (workflow-related problems) Interface (system ports related problems) Requirement (specification related problems)                                                                                                                                                            | Electrical (IC netlist and schematics abstrac  | tion view)       |

| Digital (discipline of digital specialists) Analog (discipline of analog specialists) Mixed (discipline of mixed-signal specialists) Extra-chip (discipline of physical chip specialists) Problems (factors that caused delivery issues) Informality (non-standardization related problems) Late action (late interactions or verification problems) Versioning (traceability and update-related problems) Information (documentation and team sync related problems) Process (workflow-related problems) Interface (system ports related problems) Requirement (specification related problems)                                                                                                                                                                                                                  | Geometrical (IC layout abstraction view)       |                  |

| Analog (discipline of analog specialists) Mixed (discipline of mixed-signal specialists) Extra-chip (discipline of physical chip specialists) Problems (factors that caused delivery issues) Informality (non-standardization related problems) Late action (late interactions or verification problems) Versioning (traceability and update-related problems) Information (documentation and team sync related problems) Process (workflow-related problems) Interface (system ports related problems) Requirement (specification related problems)                                                                                                                                                                                                                                                              | Disciplines (group of people with specific exp | pertise)         |